# 8-bit Enhanced USB MCU CH552/CH551

Datasheet

Version: 1F

<a href="http://wch.cn">http://wch.cn</a>

#### 1. Overview

CH552 is an enhanced E8051 core MCU compatible with MCS51 instruction set. 79% of its instructions are single-byte single-cycle instructions, and the average instruction speed is  $8 \sim 15$  times faster than that of the standard MCS51.

CH552 supports the maximum 24MHz system clock frequency, and has built-in 16K program memory ROM, 256-byte internal iRAM and 1K-byte internal xRAM. xRAM supports direct memory access (DMA).

CH552 has built-in analog-to-digital converter (ADC), touch key capacitance detection, 3 sets of timers, signal capture, PWM, 2 UARTs, SPI, USB device controller and full-speed transceiver and other function modules.

CH551 is a simplified version of CH552. The program memory ROM is 10K, the on-chip xRAM is 512 bytes, the asynchronous serial port is only UART0, the package form is only SOP16, the touch key only has 4 channels, and ADC analog-digital conversion module and USB type-C module are removed, and others are the same as those of CH552. Please directly refer to CH552 datasheet and materials.

| Product | Program<br>ROM | RAM  | DataFlash | USB<br>device | type-C       | Timer  | PWM    | UART | SPI          | ADC        | Touch key  |

|---------|----------------|------|-----------|---------------|--------------|--------|--------|------|--------------|------------|------------|

| CH552   | 16KB           | 1280 | 120       | Full/low      | Configurable |        | 2 4-   | 2    | N(4/-1       | 4 channels | 6 channels |

| CH551   | 10KB           | 768  | 128       | speed         | None         | 3 sets | 2 sets | 1    | Master/slave | None       | 4 channels |

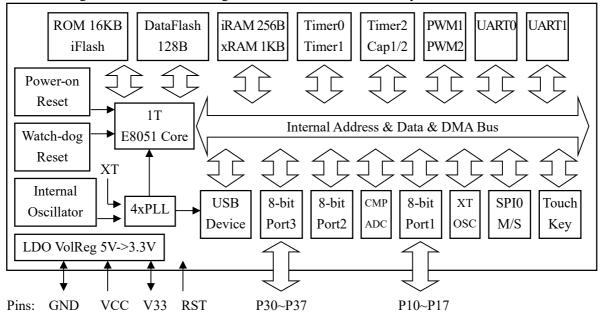

The following is the internal block diagram of CH552, for reference only.

#### 2. Features

- ◆ Core: Enhanced E8051 core compatible with MCS51 command set, 79% of its commands are single-byte single-cycle commands, and the average command speed is 8 ~ 15 times faster than that of the standard MCS51, with special XRAM data fast copy command, and double DPTR pointers.

- ROM: Non-volatile memory ROM that can be programmed for many times, with the capacity of 16KB, can all be used for program storage. Or it can be divided into a 14KB program storage area and a 2KB BootLoader/ISP program area.

- DataFlash: 128-byte non-volatile data memory that can be erased for multiple times and supports rewrite data in unit of byte.

- RAM: 256-byte internal iRAM, which can be used for fast temporary storage of data and stack. 1KB on-chip xRAM, which can be used for temporary storage of large amount of data and direct memory access (DMA).

- USB: Built-in USB controller and USB transceiver, support USB-Device mode, support USB type-C

master-slave detection, support USB 2.0 full-speed (12Mbps) and low-speed (1.5Mbps) traffic.

Support data packet of up to 64 bytes, built-in FIFO, and support DMA.

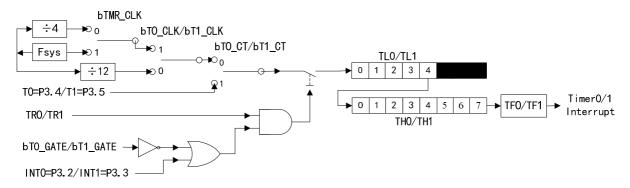

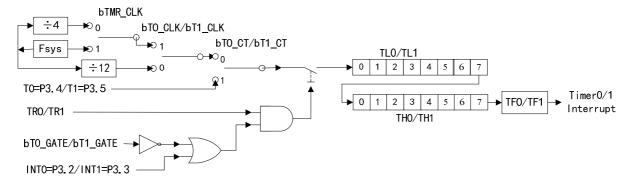

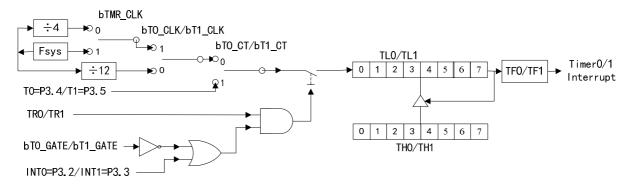

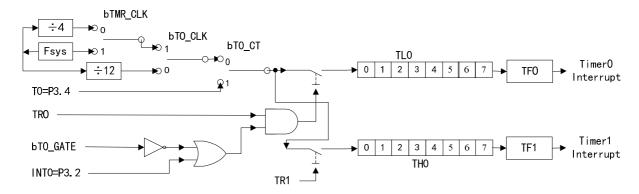

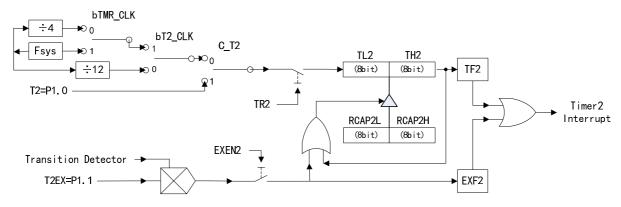

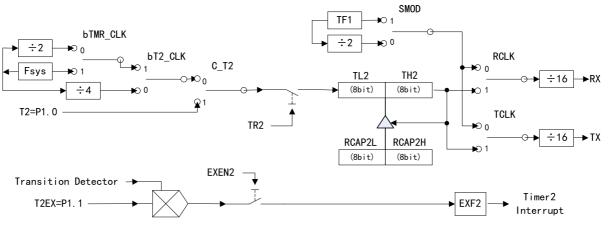

- Timer: 3 sets of timers (T0/T1/T2), which are standard MCS51 timers.

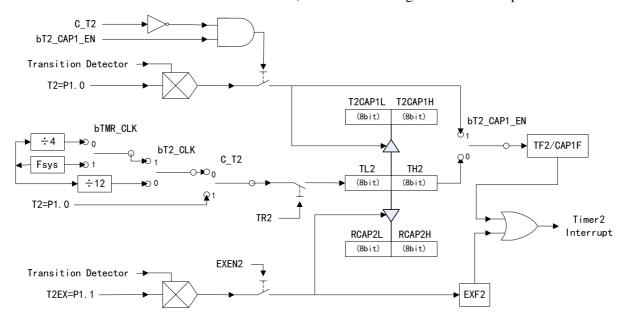

- Capture: Timer T2 is extended to support 2-channel signal capture.

- PWM: 2 PWM outputs, PWM1 and PWM2, are 2-channel 8-bit PWM output.

- UART: 2 sets of UARTs. Both support higher communication baud rate. UART0 is a standard MCS51 serial port.

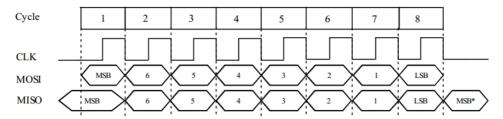

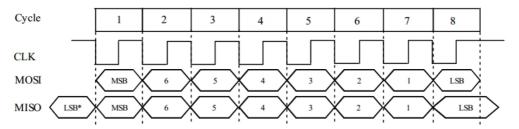

- SPI: The SPI controller has built-in FIFO, and the clock frequency can reach half of the system

dominant frequency Fsys. It supports simplex multiplex of serial data input and output, and

Master/Slave mode.

- ADC: 4-channel 8-bit A/D converter. It supports voltage comparison.

- Touch-key: 6-channel capacitance detection. It supports up to 15 touchkeys, and supports independent timing interrupt.

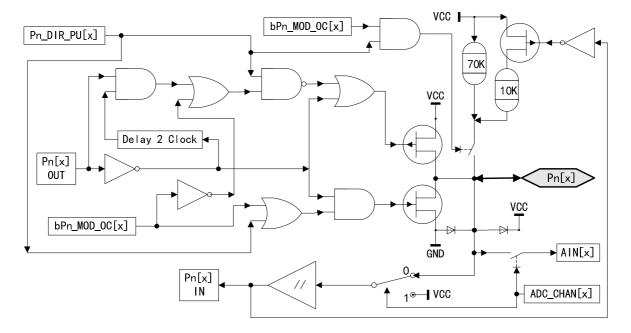

- GPIO: Up to 17 GPIO pins (including XI/XO and RST as well as USB signal pins).

- Interrupt: It supports 14 sets of interrupt signal sources, including 6 sets of interrupts compatible with the standard MCS51 (INT0, T0, INT1, T1, UART0, T2), and 8 sets of extended interrupts (SPI0, TKEY, USB, ADC, UART1, PWMX, GPIO, WDOG). And GPIO interrupt can be selected from 7 pins.

- Watch-Dog: 8-bit presettable watchdog timer WDOG, support timing interrupt.

- Reset: 4 kinds of reset signal sources. Built-in power on reset, software reset, watchdog overflow reset and optional pin external input reset.

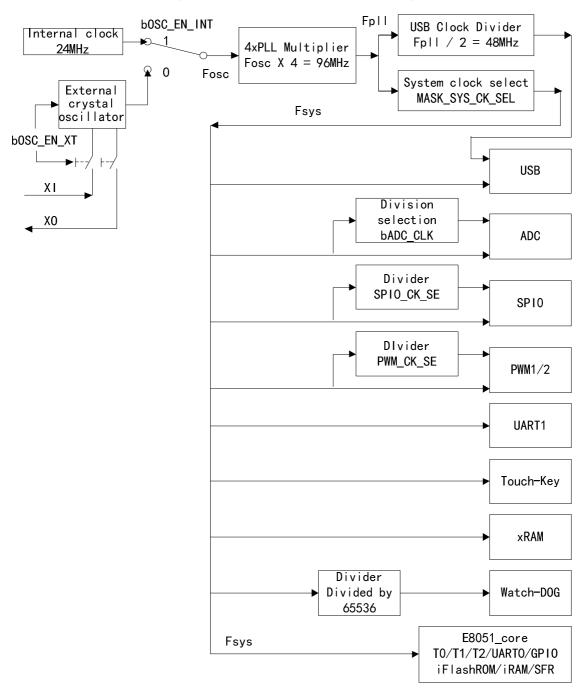

- Clock: Built-in 24MHz clock source, which can support external crystals by multiplexing GPIO pins.

- Power: Built-in 5V to 3.3V low dropout voltage regulator. It supports 5V or 3.3V or even 2.8V supply voltage. Support low-power sleep mode and external wake-up of USB, UART0, UART1, SPI0 and part of GPIOs.

- Built-in unique ID.

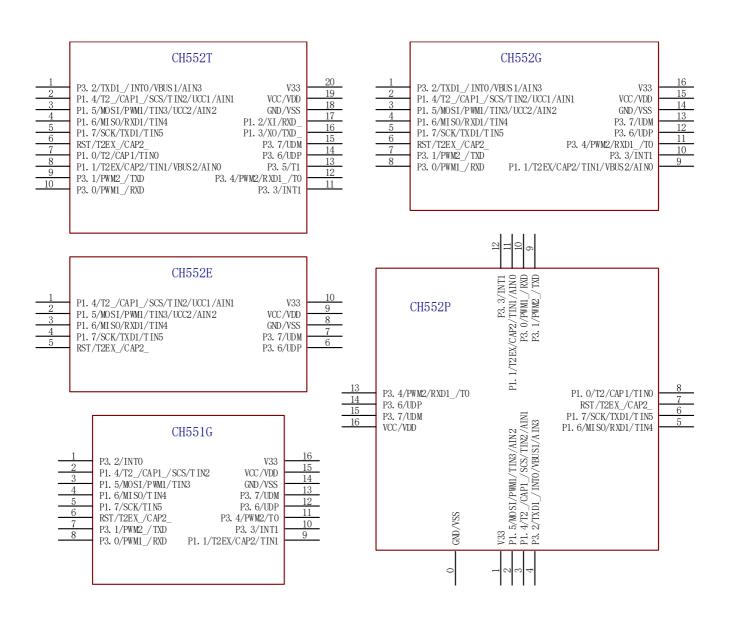

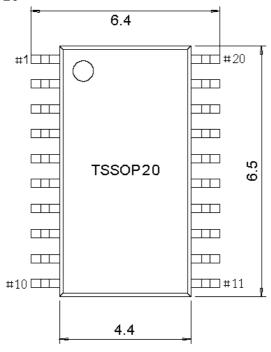

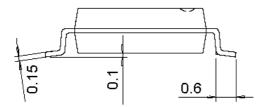

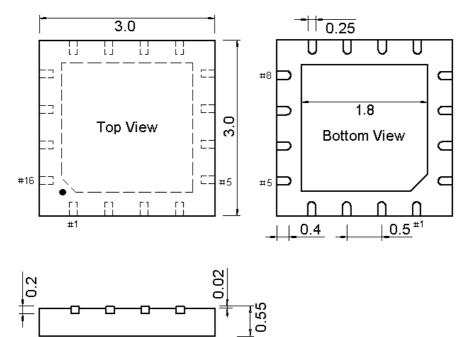

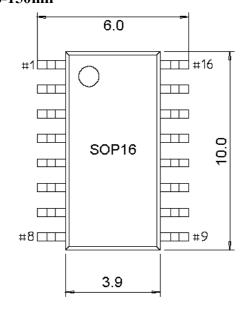

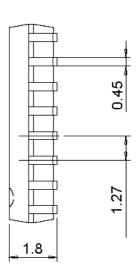

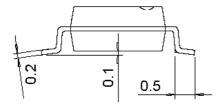

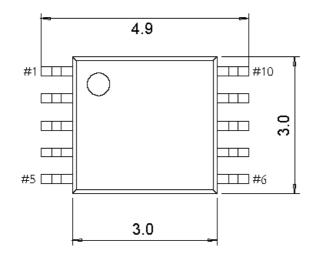

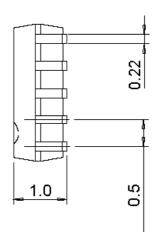

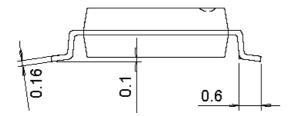

# 3. Package

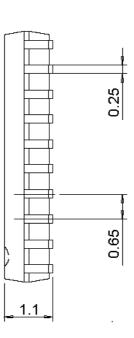

| Package  | Body size |        | Lead pitch |         | Description                            | Part No. |

|----------|-----------|--------|------------|---------|----------------------------------------|----------|

| TSSOP-20 | 4.40mm    | 173mil | 0.65mm     | 25mil   | Thin shrink small outline 20-pin patch | СН552Т   |

| SOP-16   | 3.9mm     | 150mil | 1.27mm     | 50mil   | Standard 16-pin patch                  | CH552G   |

| QFN-16   | 3*3mm     |        | 0.50mm     | 19.7mil | Quad no-lead 16-pin                    | CH552P   |

| MSOP-10  | 3.0mm     | 118mil | 0.50mm     | 19.7mil | Micro small outline 16-pin patch       | CH552E   |

| SOP-16   | 3.9mm     | 150mil | 1.27mm     | 50mil   | Standard 16-pin patch                  | CH551G   |

# 4. Pin definitions

| Pin No. |       | Pin       | Alternate |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                |

|---------|-------|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP20 | SOP16 | QFN16     |           | (Left function priority)                                                                                                                                                                                                                                                                                      | Other function description                                                                                                                                                                                                                                     |

| 19      | 15    | 16        | VCC       | VDD                                                                                                                                                                                                                                                                                                           | Power input, requires an external 0.1uF power decoupling capacitor.                                                                                                                                                                                            |

| 20      | 16    | 1         | V33       |                                                                                                                                                                                                                                                                                                               | Internal USB power regulator output and internal USB power input, When supply voltage is less than 3.6V, connect with VCC to input external power supply. When supply voltage is greater than 3.6V, connect with an external 0.1uF power decoupling capacitor. |

| 18      | 14    | 0<br>EPAD | GND       | VSS                                                                                                                                                                                                                                                                                                           | Common ground.                                                                                                                                                                                                                                                 |

| 6       | 6     | 7         | RST       | RST/T2EX_/CAP2_                                                                                                                                                                                                                                                                                               | The pin with underscore suffix is a mapping of the                                                                                                                                                                                                             |

| 7       | -     | 8         | P1.0      | T2/CAP1/TIN0                                                                                                                                                                                                                                                                                                  | homonymous pin with no underscore.                                                                                                                                                                                                                             |

| 8       | 9     | 11        | P1.1      | T2EX/CAP2/TIN1<br>/VBUS2/AIN0                                                                                                                                                                                                                                                                                 | RST pin built-in pull-down resistor. Other GPIO have pull-up resistor in default.                                                                                                                                                                              |

| 17      | -     | -         | P1.2      | XI/RXD                                                                                                                                                                                                                                                                                                        | RST: External reset input.                                                                                                                                                                                                                                     |

| 16      | -     | -         | P1.3      | XO/TXD                                                                                                                                                                                                                                                                                                        | T2: External count input/clock output of                                                                                                                                                                                                                       |

| 2       | 2     | 3         | P1.4      | T2_/CAP1_/SCS<br>/TIN2/UCC1/AIN1                                                                                                                                                                                                                                                                              | Timer/Counter 2.  T2EX: Reload/capture input of Timer/Counter 2.                                                                                                                                                                                               |

| 3       | 3     | 2         | P1.5      | MOSI/PWM1/TIN3<br>/UCC2/AIN2                                                                                                                                                                                                                                                                                  | CAP1, CAP2: Capture input 1, 2 of Timer/Counter 2. TIN0 ~ TIN5: Touch key capacitance detection input of channel 0# ~ 5#.                                                                                                                                      |

| 4       | 4     | 5         | P1.6      | MISO/RXD1/TIN4                                                                                                                                                                                                                                                                                                | AIN0 ~ AIN3: ADC analog signal input of channel                                                                                                                                                                                                                |

| 5       | 5     | 6         | P1.7      | SCK/TXD1/TIN5                                                                                                                                                                                                                                                                                                 | $0\% \sim 3\%$ .                                                                                                                                                                                                                                               |

| 10      | 8     | 10        | P3.0      | PWM1_/RXD                                                                                                                                                                                                                                                                                                     | UCC1, UCC2: USB type-C bidirectional                                                                                                                                                                                                                           |

| 9       | 7     | 9         | P3.1      | PWM2_/TXD                                                                                                                                                                                                                                                                                                     | configuration channel.                                                                                                                                                                                                                                         |

| 1       | 1     | 4         | P3.2      | TXD1_/INT0<br>/VBUS1/AIN3                                                                                                                                                                                                                                                                                     | VBUS1, VBUS2: USB type-C bus voltage detection input.                                                                                                                                                                                                          |

| 11      | 10    | 12        | P3.3      | INT1                                                                                                                                                                                                                                                                                                          | XI, XO: External crystal oscillation input, inverted                                                                                                                                                                                                           |

| 12      | 11    | 13        | P3.4      | PWM2/RXD1_/T0                                                                                                                                                                                                                                                                                                 | input.                                                                                                                                                                                                                                                         |

| 13      | -     | -         | P3.5      | T1                                                                                                                                                                                                                                                                                                            | RXD, TXD: UART0 serial data input, serial data output.                                                                                                                                                                                                         |

| 14      | 12    | 14        | P3.6      | UDP                                                                                                                                                                                                                                                                                                           | SCS, MOSI, MISO, SCK: SPI0 interface, SCS is chip                                                                                                                                                                                                              |

| 15      |       |           | UDM       | selection input, MOSI is host output/slave input, MISO is host input/slave output, SCK is serial clock. PWM1, PWM2: PWM1 output, PWM2 output. RXD1, TXD1: UART1 serial data input, serial data output. INT0, INT1: External interrupt 0, external interrupt 1 input. T0, T1: Timer 0, Timer 1 external input. |                                                                                                                                                                                                                                                                |

|  | UDM and UDP: D- and D+ signal terminals of USB      |

|--|-----------------------------------------------------|

|  | device.                                             |

|  | Note: P3.6 and P3.7 internally use V33 as I/O power |

|  | so the high level of the input and output can only  |

|  | reach the voltage V33, and 5V is not supported      |

Note: The USB transceiver is designed built-in based on USB2.0. The P3.6 pin and the P3.7 pin cannot be connected to resistors in series when they are used for USB.

## 5. Special function register (SFR)

The following abbreviations may be used in this datasheet to describe the registers:

| Abbreviation | Description                                                     |

|--------------|-----------------------------------------------------------------|

| RO           | Software can only read these bits.                              |

| WO           | Software can only write to this bit. The read value is invalid. |

| RW           | Software can read and write to these bits.                      |

| Н            | End with it to indicate a hexadecimal number                    |

| В            | End with it to indicate a binary number                         |

#### 5.1 SFR introduction and address distribution

CH552 controls, manages the device, and sets the working mode with a special function register (SFR).

SFR occupies 80H-FFH address range of the internal data storage space and can only be accessed by direct address commands. Registers with the address x0h and x8h can be accessed by bits to avoid modifying the values of other bits when accessing a specific bit. Other registers with the addresses that are not the multiple of 8 can only be accessed by bytes.

Some SFRs can be written only in safe mode, while they can be read only in unsafe mode, such as: GLOBAL CFG, CLOCK CFG, WAKE CTRL.

Some SFRs have one or more aliases, for example: SPI0 CK SE/SPI0 S PRE.

Some addresses correspond to several independent SFRs, for example: SAFE\_MOD/CHIP\_ID, ROM CTRL/ROM STATUS.

CH552 contains the 8051 standard SFR register, and other device control registers are added. See the table below for SFRs.

Table 5.1 Special function registers

|      |            |            |            | •                        | <u> </u>   |            |            |            |

|------|------------|------------|------------|--------------------------|------------|------------|------------|------------|

| SFR  | 0, 8       | 1, 9       | 2, A       | 3, B                     | 4, C       | 5, D       | 6, E       | 7, F       |

| 0xF8 | SPI0_STAT  | SPI0_DATA  | SPI0_CTRL  | SPIO_CK_SE<br>SPIO_S_PRE | SPI0_SETUP |            | RESET_KEEP | WDOG_COUNT |

| 0xF0 | В          |            |            |                          |            |            |            |            |

| 0xE8 | IE_EX      | IP_EX      | UEP4_1_MOD | UEP2_3_MOD               | UEP0_DMA_L | UEP0_DMA_H | UEP1_DMA_L | UEP1_DMA_H |

| 0xE0 | ACC        | USB_INT_EN | USB_CTRL   | USB_DEV_AD               | UEP2_DMA_L | UEP2_DMA_H | UEP3_DMA_L | UEP3_DMA_H |

| 0xD8 | USB_INT_FG | USB_INT_ST | USB_MIS_ST | USB_RX_LEN               | UEP0_CTRL  | UEP0_T_LEN | UEP4_CTRL  | UEP4_T_LEN |

| 0xD0 | PSW        | UDEV_CTRL  | UEP1_CTRL  | UEP1_T_LEN               | UEP2_CTRL  | UEP2_T_LEN | UEP3_CTRL  | UEP3_T_LEN |

| 0xC8 | T2CON      | T2MOD      | RCAP2L     | RCAP2L                   | TL2        | TH2        | T2CAP1L    | T2CAP1H    |

| 0xC0 | SCON1    | SBUF1      | SBAUD1    | TKEY_CTRL | TKEY_DATL  | TKEY_DATH  | PIN_FUNC            | GPIO_IE    |

|------|----------|------------|-----------|-----------|------------|------------|---------------------|------------|

| 0xB8 | IP       | CLOCK_CFG  |           |           |            |            |                     |            |

| 0xB0 | Р3       | GLOBAL_CFG |           |           |            |            |                     |            |

| 0xA8 | IE       | WAKE_CTRL  |           |           |            |            |                     |            |

| 0xA0 | P2       | SAFE_MOD   | XBUS AUX  |           |            |            |                     |            |

| UAAU | 1 2      | CHIP_ID    | ADOS_AOA  |           |            |            |                     |            |

| 0x98 | SCON     | SBUF       | ADC_CFG   | PWM_DATA2 | PWM_DATA1  | PWM_CTRL   | PWM_CK_SE           | ADC_DATA   |

| 0x90 | P1       | USB_C_CTRL | P1_MOD_OC | P1_DIR_PU |            |            | P3_MOD_OC           | P3_DIR_PU  |

| 0x88 | TCON     | TMOD       | TL0       | TL1       | TH0        | TH1        | ROM_DATA_L          | ROM_DATA_H |

| 0x80 | ADC_CTRL | SP         | DPL       | DPH       | ROM_ADDR_L | ROM_ADDR_H | ROM_CTRL ROM_STATUS | PCON       |

Notes: (1) Those in red text can be accessed by bits;

(2) The following table shows the corresponding description of different color boxes

| <br>the results and the control of the c |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SPI0 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ADC register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Touch-Key registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| USB register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timer/counter2 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Port setting register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PWM1 and PWM2 registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| UART1 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Flash-ROM register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# 5.2 SFR classification and reset value

Table 5.2 SFR description and reset value

| Function<br>Classification | Name       | Address | Description                                         | Reset value |

|----------------------------|------------|---------|-----------------------------------------------------|-------------|

|                            | В          | F0h     | B register                                          | 0000 0000Ь  |

|                            | ACC        | E0h     | Accumulator                                         | 0000 0000Ь  |

|                            | PSW        | D0h     | Program status word register                        | 0000 0000Ь  |

|                            |            |         | Global configuration register (CH552<br>Bootloader) | 1010 0000Ь  |

| System                     | CLODAL CEC | B1h     | Global configuration register (CH552 application)   | 1000 0000Ь  |

| setting<br>registers       | GLOBAL_CFG |         | Global configuration register (CH551<br>Bootloader) | 1110 0000Ь  |

|                            |            |         | Global configuration register (CH551 application)   | 1100 0000Ь  |

|                            | CHID ID    | A 11-   | ID code of CH552 (read only)                        | 0101 0010b  |

|                            | CHIP_ID    | Alh     | ID code of CH551 (read only)                        | 0101 0001b  |

|                            | SAFE_MOD   | A1h     | Safe mode control register (write only)             | 0000 0000ь  |

| DPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | DPH            | 83h | Data address pointer high 8 bits        | 0000 0000b |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-----|-----------------------------------------|------------|

| DPTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                |     |                                         |            |

| SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                |     | _                                       |            |

| Clock, sleep and power   RESET_KEEP   FEh   Reset keep register (in power on reset state)   0000 0000b   RESET_KEEP   FEh   Reset keep register (in power on reset state)   0000 0000b   CLOCK_CFG   B9h   System clock configuration register   0000 0000b   CLOCK_CFG   B9h   System clock configuration register   0000 0000b   PCON   87h   Power control register (in power on reset state)   0000 0000b   PCON   87h   Power control register (in power on reset state)   0000 0000b   PCON   Reset    |             | SP             |     | Stack pointer                           |            |

| RESET_KEEP   FEb   Reset keep register (in power on reset state)   0000 0000b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clock sleen | WDOG COUNT     | FFh |                                         | 0000 0000b |

| Supply control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | _              | FEh |                                         |            |

| WAKE_CTRL   A9h   Sleep wakeup control register   0000 00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •           |                | B9h |                                         | 1000 0011b |

| PCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | WAKE CTRL      | A9h |                                         | 0000 0000b |

| P_EX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | registers   | _              | 87h |                                         | 0001 0000b |

| Interrupt control control control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             | IP EX          | E9h |                                         | 0000 0000b |

| control registers         GPIO_IE         C7h         GPIO interrupt enable register         0000 00000 0000 0000 0000 0000 0000 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interrupt   | _              | E8h |                                         | 0000 0000b |

| IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •           | GPIO_IE        | C7h | GPIO interrupt enable register          | 0000 0000b |

| ROM_DATA_H   8Fh   Flash-ROM data register high byte   RXXX XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | registers   | IP             | B8h | Interrupt priority control register     | 0000 0000b |

| ROM_DATA_L   8Eh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             | IE             | A8h | Interrupt enable register               | 0000 0000b |