# 7 シリーズ FPGA データシート: 概要

DS180 (v2.5) 2017 年 8 月 1 日

Production 製品仕様

### 概要

4 つの FPGA ファミリで構成されるザイリンクス 7 シリーズ FPGA は、低コスト、スモール フォーム ファクター、コスト重視、あるいは量産向けアプリケーションから、超高性能コネクティビティ帯域幅、ロジック容量、信号処理性能を必要とする最も要件の厳しいアプリケーションまであらゆる分野のシステム要件に対応します。 7 シリーズ FPGA ファミリは次のとおりです。

- Spartan-7ファミリ: 低コスト、最も低い消費電力、高い I/O 性能 を 実現するよう最適化されています。PCB フットプリントを最小にす るための、低コストかつ非常に小型のパッケージが用意されていま す。

- Artix®-7 ファミリ: シリアルトランシーバーを使用したり、DSPやロジックに高いスループットを求める低消費電力アプリケーション向けに最適化されています。高いスループット、コスト重視のアプリケーション向けに最も低い BOM コストを提供します。

- Kintex®-7 ファミリ: 前世代の FPGA と比較して 2 倍の対価格性能 を実現するよう最適化された新しいクラスの FPGA です。

- Virtex®-7 ファミリ: 2 倍のシステム性能と容量を実現するよう最適 化された最高性能の FPGA です。これは SSI (スタックド シリコン インターコネクト) テクノロジによって実現された最高性能を備え るデバイスです。

高性能かつ低消費電力 (HPL) の 28nm High-k メタル ゲート (HKMG) プロセス テクノロジを採用した 7 シリーズ FPGA は、2.9Tb/s の I/O 帯域幅、200 万ロジック セル、5.3TMAC/s の DSP デジタル信号処理をサポートする、従来にないシステム性能と 50% の消費電力削減を同時に実現した、ASSP や ASIC に置き換わる完全なプログラマブル デバイスです。

## 7シリーズ FPGA の特長

- 完全な6入力のルックアップテーブル(LUT)テクノロジをベースとする最先端の高性能 FPGAロジックは、分散メモリとしても構成可能

- オンチップのデータ バッファー用に FIFO ロジックを内蔵する 36Kb デュアル ポート ブロック RAM

- 最高 1,866Mb/s の DDR3 インターフェイスをサポートする高性能 SelectIO<sup>TM</sup> テクノロジ

- 600Mb/s から最高 6.6Gb/s ~ 28.05Gb/s のレートをサポートする内蔵マルチギガビット トランシーバーによる高速シリアル コネクティビティは、チップ間インターフェイス用に低電力モードも提供

- ユーザーが設定可能なアナログ インターフェイス (XADC) は、温度 および電源計測用のオンチップ センサーを持つ 12 ビット、1MSPS の汎用アナログ/デジタル コンバーターを 2 つ備えている

- $25 \times 18$  乗算器、48 ビット アキュムレータ、および対称係数フィルタリングを含む高度なフィルター処理用の前置加算器 (乗算器前段の加算器) を備える DSP スライス

- PLL (位相ロック ループ) と MMCM (ミックスド モード クロック マネージャー) ブロックを組み合わせた CMT (クロック マネージメント タイル) によって高精度で低ジッターのクロック制御

- 最高で x 8 Gen3 のエンドポイントおよびルート ポート デザインを サポートする PCI Express® (PCIe) 用統合ブロック

- 汎用メモリ、HMAC/SHA-256 認証を用いた 256 ビット AES 暗号化、内蔵型 SEU 検出および訂正のサポートを含む多様なコンフィギュレーション オプション

- 低コストのワイヤボンド、リッドなしのフリップチップおよびシグナル インテグリティに優れたフリップチップ パッケージは同一パッケージのファミリ間で簡単に移行可能。すべてのパッケージは鉛フリーで提供され、一部は鉛パッケージでも入手可能

- 高性能かつ最も低い消費電力を実現するよう設計された 28nm、 HKMG、HPL プロセス テクノロジを採用し、1.0V のコア電圧と 0.9V の低消費電力オプションをサポート

#### 表 1: 7 シリーズ ファミリの機能の比較

| 機能 (最大)                 | Spartan-7   | Artix-7     | Kintex-7    | Virtex-7    |

|-------------------------|-------------|-------------|-------------|-------------|

| ロジック セル                 | 102K        | 215K        | 478K        | 1,955K      |

| ブロック RAM <sup>(1)</sup> | 4.2Mb       | 13Mb        | 34Mb        | 68Mb        |

| DSP スライス                | 160         | 740         | 1,920       | 3,600       |

| DSP 性能 <sup>(2)</sup>   | 176GMAC/s   | 929GMAC/s   | 2,845GMAC/s | 5,335GMAC/s |

| トランシーバー                 | _           | 16          | 32          | 96          |

| トランシーバー速度               | _           | 6.6 Gb/s    | 12.5Gb/s    | 28.05Gb/s   |

| シリアル バンド幅               | _           | 211Gb/s     | 800Gb/s     | 2,784Gb/s   |

| PCIe インターフェイス           | _           | x4 Gen2     | x8 Gen2     | x8 Gen3     |

| メモリ インターフェイス            | 800Mb/s     | 1,066Mb/s   | 1,866Mb/s   | 1,866Mb/s   |

| I/O ピン                  | 400         | 500         | 500         | 1,200       |

| I/O 電圧                  | 1.2V ∼ 3.3V | 1.2V ∼ 3.3V | 1.2V ∼ 3.3V | 1.2V ∼ 3.3V |

© Copyright 2015-2017 Xilinx, Inc. Xilinx、Xilinx のロゴ、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq、およびこの文書に含まれるその他の指定されたブランドは、米国およびその他各国のザイリンクス社の商標です。すべてのその他の商標は、それぞれの保有者に帰属します。

本資料は表記のバージョンの英語版を翻訳したもので、内容に相違が生じる場合には原文を優先します。 資料によっては英語版の更新に対応していないものがあります。 日本語版は参考用としてご使用の上、最新情報につきましては、必ず最新英語版をご参照ください。

### 表 1:7 シリーズ ファミリの機能の比較 (続き)

| 機能 (最大)     | Spartan-7   | Artix-7                      | Kintex-7                    | Virtex-7        |

|-------------|-------------|------------------------------|-----------------------------|-----------------|

| パッケージ オプション | 低コスト、ワイヤボンド | 低コスト、ワイヤボンド、<br>リッドなしフリップチップ | リッドなしフリップチップ<br>と高性能フリップチップ | 最高性能<br>フリップチップ |

#### 注記:

- 1. 分散 RAM の形で追加のメモリが使用可能です。

- 2. DSP の最大処理速度は、対称フィルターを実装して算出しています。

# Spartan-7 FPGA の機能一覧

### 表 2: Spartan-7 FPGA の機能一覧

|         | 50° 45     | С      | LB               | DSP         | ブロック | RAMブ | ロック <sup>(3)</sup> |                    |      |    | XADC | <b>#</b> \ 1/O              | 84-            |

|---------|------------|--------|------------------|-------------|------|------|--------------------|--------------------|------|----|------|-----------------------------|----------------|

| デバイス    | ロジック<br>セル | スライス数  | 最大分散<br>RAM (Kb) | スライス<br>(2) | 18Kb | 36Kb | 最大<br>(Kb)         | CMT <sup>(4)</sup> | PCle | GT | ブロック | 総 I/O<br>バンク <sup>(5)</sup> | 最大ユー<br>ザー I/O |

| XC7S6   | 6,000      | 938    | 70               | 10          | 10   | 5    | 180                | 2                  | 0    | 0  | 0    | 2                           | 100            |

| XC7S15  | 12,800     | 2,000  | 150              | 20          | 20   | 10   | 360                | 2                  | 0    | 0  | 0    | 2                           | 100            |

| XC7S25  | 23,360     | 3,650  | 313              | 80          | 90   | 45   | 1,620              | 3                  | 0    | 0  | 1    | 3                           | 150            |

| XC7S50  | 52,160     | 8,150  | 600              | 120         | 150  | 75   | 2,700              | 5                  | 0    | 0  | 1    | 5                           | 250            |

| XC7S75  | 76,800     | 12,000 | 832              | 140         | 180  | 90   | 3,240              | 8                  | 0    | 0  | 1    | 8                           | 400            |

| XC7S100 | 102,400    | 16,000 | 1,100            | 160         | 240  | 120  | 4,320              | 8                  | 0    | 0  | 1    | 8                           | 400            |

#### 注記:

- 1. 7シリーズ FPGA の各スライスには、4つの LUT と 8つのフリップフロップが含まれ、一部のスライスでのみ LUT を分散 RAM または SRL として使用できます。

- 2. 各 DSP スライスには 25×18 乗算器、加算器、アキュムレータが 1 つずつ含まれます。

- 3. ブロック RAM は基本的に 36Kb ですが、2 つの独立した 18Kb ブロックとしても使用できます。

- 4. 各 CMT には MMCM と PLL が 1 つずつ含まれます。

- 5. コンフィギュレーション バンク 0 は含まれません。

### 表 3: Spartan-7 デバイスとパッケージの各組み合わせにおける最大 I/O 数

| パッケージ        | CPGA196               | CSGA225               | CSGA324               | FTGB196               | FGGA484               | FGGA676               |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| サイズ (mm)     | 8 x 8                 | 13 x 13               | 15 x 15               | 15 x 15               | 23 x 23               | 27 x 27               |

| ボール ピッチ (mm) | 0.5                   | 0.8                   | 0.8                   | 1.0                   | 1.0                   | 1.0                   |

| デバイス         | HR I/O <sup>(1)</sup> |

| XC7S6        | 100                   | 100                   |                       | 100                   |                       |                       |

| XC7S15       | 100                   | 100                   |                       | 100                   |                       |                       |

| XC7S25       |                       | 150                   | 150                   | 100                   |                       |                       |

| XC7S50       |                       |                       | 210                   | 100                   | 250                   |                       |

| XC7S75       |                       |                       |                       |                       | 338                   | 400                   |

| XC7S100      |                       |                       |                       |                       | 338                   | 400                   |

#### 注記:

1. HR は High Range I/O で、1.2V から 3.3V の I/O 電圧をサポートします。

# Artix-7 FPGA の機能一覧

#### 表 4: Artix-7 FPGA の機能一覧

|          | ロジック    |         | ラブルロジック<br>ク (CLB) | DSP48E1 | ブロック | RAM ブ | ロック <sup>(3)</sup> | CMT <sup>(4)</sup> | PCIe <sup>(5)</sup> | GTP | XADC     | 総 I/O バン         | 最大ユー                          |

|----------|---------|---------|--------------------|---------|------|-------|--------------------|--------------------|---------------------|-----|----------|------------------|-------------------------------|

| デバイス     | セル      | スラ(1)ス数 | 最大分散<br>RAM (Kb)   | スライス    | 18Kb | 36Kb  | 最大<br>(Kb)         | CIVITY             | r Cie(e)            | GIF | ブロッ<br>ク | ク <sup>(6)</sup> | 最大ユー<br>ザー I/O <sup>(7)</sup> |

| XC7A12T  | 12,800  | 2,000   | 171                | 40      | 40   | 20    | 720                | 3                  | 1                   | 2   | 1        | 3                | 150                           |

| XC7A15T  | 16,640  | 2,600   | 200                | 45      | 50   | 25    | 900                | 5                  | 1                   | 4   | 1        | 5                | 250                           |

| XC7A25T  | 23,360  | 3,650   | 313                | 80      | 90   | 45    | 1,620              | 3                  | 1                   | 4   | 1        | 3                | 150                           |

| XC7A35T  | 33,280  | 5,200   | 400                | 90      | 100  | 50    | 1,800              | 5                  | 1                   | 4   | 1        | 5                | 250                           |

| XC7A50T  | 52,160  | 8,150   | 600                | 120     | 150  | 75    | 2,700              | 5                  | 1                   | 4   | 1        | 5                | 250                           |

| XC7A75T  | 75,520  | 11,800  | 892                | 180     | 210  | 105   | 3,780              | 6                  | 1                   | 8   | 1        | 6                | 300                           |

| XC7A100T | 101,440 | 15,850  | 1,188              | 240     | 270  | 135   | 4,860              | 6                  | 1                   | 8   | 1        | 6                | 300                           |

| XC7A200T | 215,360 | 33,650  | 2,888              | 740     | 730  | 365   | 13,140             | 10                 | 1                   | 16  | 1        | 10               | 500                           |

#### 注記:

- 1. 7 シリーズ FPGA の各スライスには、4 つの LUT と 8 つのフリップフロップが含まれ、一部のスライスでのみ LUT を分散 RAM または SRL として使用できます。

- 2. 各 DSP スライスには  $25 \times 18$  乗算器、加算器、アキュムレータが 1 つずつ含まれます。

- 3. ブロック RAM は基本的に 36Kb ですが、2 つの独立した 18Kb ブロックとしても使用できます。

- 4. 各 CMT には MMCM と PLL が 1 つずつ含まれます。

- 5. Artix-7 FPGA の PCI Express 用インターフェイス ブロックは最高 ×4 Gen 2 をサポートします。

- 5. コンフィギュレーション バンク 0 は含まれません。

- 7. 記載の数値に GTP トランシーバーは含まれません。

#### 表 5: Artix-7 デバイスとパッケージの各組み合わせにおける最大 I/O 数

| (1)ッケージ             | CPG        | 9236                     | CPC        | 3238                     | CSG  | 324                      | CSC | 325                      | FTG        | 256                      | SBG  | G484                     | FGG <sup>4</sup> | 484 <sup>(2)</sup>       | FBG <sup>2</sup> | 484 <sup>(2)</sup>       | FGG  | 676 <sup>(3)</sup>       | FBG6 | 676 <sup>(3)</sup>       | FFG  | 1156                     |

|---------------------|------------|--------------------------|------------|--------------------------|------|--------------------------|-----|--------------------------|------------|--------------------------|------|--------------------------|------------------|--------------------------|------------------|--------------------------|------|--------------------------|------|--------------------------|------|--------------------------|

| サイズ<br>(mm)         | 10 3       | k 10                     | 10 :       | x 10                     | 15 : | <b>&lt;</b> 15           | 15  | x 15                     | 17 :       | x 17                     | 19 : | x 19                     | 23 >             | x 23                     | 23 >             | x 23                     | 27 > | x 27                     | 27 > | k 27                     | 35 > | 35                       |

| ボール ピッ<br>チ<br>(mm) | 0          | .5                       | 0          | .5                       | 0    | .8                       | 0   | .8                       | 1          | .0                       | 0    | .8                       | 1.               | .0                       | 1.               | .0                       | 1.   | .0                       | 1.   | .0                       | 1.   | 0                        |

| デバイス                | GTP<br>(4) | I/O<br>HR <sup>(5)</sup> | GTP<br>(4) | I/O<br>HR <sup>(5)</sup> | GTP  | I/O<br>HR <sup>(5)</sup> | GTP | I/O<br>HR <sup>(5)</sup> | GTP<br>(4) | I/O<br>HR <sup>(5)</sup> | GTP  | I/O<br>HR <sup>(5)</sup> | GTP<br>(4)       | I/O<br>HR <sup>(5)</sup> | GTP              | I/O<br>HR <sup>(5)</sup> | GTP  | I/O<br>HR <sup>(5)</sup> | GTP  | I/O<br>HR <sup>(5)</sup> | GTP  | I/O<br>HR <sup>(5)</sup> |

| XC7A12T             |            |                          | 2          | 112                      |      |                          | 2   | 150                      |            |                          |      |                          |                  |                          |                  |                          |      |                          |      |                          |      |                          |

| XC7A15T             | 2          | 106                      |            |                          | 0    | 210                      | 4   | 150                      | 0          | 170                      |      |                          | 4                | 250                      |                  |                          |      |                          |      |                          |      |                          |

| XC7A25T             |            |                          | 2          | 112                      |      |                          | 4   | 150                      |            |                          |      |                          |                  |                          |                  |                          |      |                          |      |                          |      |                          |

| XC7A35T             | 2          | 106                      |            |                          | 0    | 210                      | 4   | 150                      | 0          | 170                      |      |                          | 4                | 250                      |                  |                          |      |                          |      |                          |      |                          |

| XC7A50T             | 2          | 106                      |            |                          | 0    | 210                      | 4   | 150                      | 0          | 170                      |      |                          | 4                | 250                      |                  |                          |      |                          |      |                          |      |                          |

| XC7A75T             |            |                          |            |                          | 0    | 210                      |     |                          | 0          | 170                      |      |                          | 4                | 285                      |                  |                          | 8    | 300                      |      |                          |      |                          |

| XC7A100T            |            |                          |            |                          | 0    | 210                      |     |                          | 0          | 170                      |      |                          | 4                | 285                      |                  |                          | 8    | 300                      |      |                          |      |                          |

| XC7A200T            |            |                          |            |                          |      |                          |     |                          |            |                          | 4    | 285                      |                  |                          | 4                | 285                      |      |                          | 8    | 400                      | 16   | 500                      |

- 1. 記載されているパッケージはすべて鉛フリーです (SBG、FBG、FFG には例外項目 No. 15 が適用される)。一部は鉛パッケージでも入手可能です。

- 2. FGG484 と FBG484 のデバイスは、フットプリントに互換性があります。

- 3. FGG676 と FBG676 のデバイスは、フットプリントに互換性があります。

- 4. CP、CS、FT、および FG パッケージの GTP トランシーバーは、最大 6.25Gb/s のデータ レートをサポートします。

- 5. HR は High Range I/O で、1.2V から 3.3V の I/O 電圧をサポートします。

## Kintex-7 FPGA の機能一覧

#### 表 6: Kintex-7 FPGA の機能一覧

|          | ロジック    |        | ギャラブル<br>ロック (CLB) | DSP   | ブロック  | カ RAM ブ | ロック <sup>(3)</sup> | CMT <sup>(4)</sup> | PCIe <sup>(5)</sup> | GTX | XADC | 総 I/O              | 最大ユー<br>ザー I/O <sup>(7)</sup> |

|----------|---------|--------|--------------------|-------|-------|---------|--------------------|--------------------|---------------------|-----|------|--------------------|-------------------------------|

| デバイス     | セル      | スライス数  | 最大分散<br>RAM (Kb)   | スライス  | 18Kb  | 36Kb    | 最大<br>(Kb)         | CIVITY             | FOIE                | GIX | ブロック | バンク <sup>(6)</sup> | ザー I/O <sup>(7)</sup>         |

| XC7K70T  | 65,600  | 10,250 | 838                | 240   | 270   | 135     | 4,860              | 6                  | 1                   | 8   | 1    | 6                  | 300                           |

| XC7K160T | 162,240 | 25,350 | 2,188              | 600   | 650   | 325     | 11,700             | 8                  | 1                   | 8   | 1    | 8                  | 400                           |

| XC7K325T | 326,080 | 50,950 | 4,000              | 840   | 890   | 445     | 16,020             | 10                 | 1                   | 16  | 1    | 10                 | 500                           |

| XC7K355T | 356,160 | 55,650 | 5,088              | 1,440 | 1,430 | 715     | 25,740             | 6                  | 1                   | 24  | 1    | 6                  | 300                           |

| XC7K410T | 406,720 | 63,550 | 5,663              | 1,540 | 1,590 | 795     | 28,620             | 10                 | 1                   | 16  | 1    | 10                 | 500                           |

| XC7K420T | 416,960 | 65,150 | 5,938              | 1,680 | 1,670 | 835     | 30,060             | 8                  | 1                   | 32  | 1    | 8                  | 400                           |

| XC7K480T | 477,760 | 74,650 | 6,788              | 1,920 | 1,910 | 955     | 34,380             | 8                  | 1                   | 32  | 1    | 8                  | 400                           |

#### 注記:

- 1. 7シリーズ FPGA の各スライスには、4つの LUT と 8つのフリップフロップが含まれ、一部のスライスでのみ LUT を分散 RAM または SRL として使用できます。

- 2. 各 DSP スライスには 25 × 18 乗算器、加算器、アキュムレータが 1 つずつ含まれます。

- 3. ブロック RAM は基本的に 36Kb ですが、2 つの独立した 18Kb ブロックとしても使用できます。

- 4. 各 CMT には MMCM と PLL が 1 つずつ含まれます。

- 5. Kintex-7 FPGA の PCI Express 用インターフェイス ブロックは最高 ×8 Gen 2 をサポートします。

- 6. コンフィギュレーション バンク 0 は含まれません。

- 7. 記載の数値に GTX トランシーバーは含まれません。

#### 表 7: Kintex-7 デバイスとパッケージの各組み合わせにおける最大 I/O 数

| パッケージ <sup>(1)</sup> | F   | BG48              | 4     | F   | BG676             | (2)   | F   | FG676             | (2)   | F   | BG900             | (3)   | F   | FG900             | (3)   | F   | FG90              | 1     | F   | FG115             | 6     |

|----------------------|-----|-------------------|-------|-----|-------------------|-------|-----|-------------------|-------|-----|-------------------|-------|-----|-------------------|-------|-----|-------------------|-------|-----|-------------------|-------|

| サイズ (mm)             | :   | 23 x 23           | 3     | :   | 27 x 27           | ,     |     | 27 x 27           | 7     |     | 31 x 31           |       | ;   | 31 x 31           |       | ;   | 31 x 31           |       | ;   | 35 x 35           | 5     |

| ボールピッチ<br>(mm)       |     | 1.0               |       |     | 1.0               |       |     | 1.0               |       |     | 1.0               |       |     | 1.0               |       |     | 1.0               |       |     | 1.0               |       |

| デバイス                 | GTX | I/                | O.    | GTX | I/                | 0     | GTX |                   |       | GTX | I/                | 0     |

| 7/1/                 | (4) | HR <sup>(5)</sup> | HP(6) | (4) | HR <sup>(5)</sup> | HP(6) | GIX | HR <sup>(5)</sup> | HP(6) | (4) | HR <sup>(5)</sup> | HP(6) | GIX | HR <sup>(5)</sup> | HP(6) | GIX | HR <sup>(5)</sup> | HP(6) | GIX | HR <sup>(5)</sup> | HP(6) |

| XC7K70T              | 4   | 185               | 100   | 8   | 200               | 100   |     |                   |       |     |                   |       |     |                   |       |     |                   |       |     |                   |       |

| XC7K160T             | 4   | 185               | 100   | 8   | 250               | 150   | 8   | 250               | 150   |     |                   |       |     |                   |       |     |                   |       |     |                   |       |

| XC7K325T             |     |                   |       | 8   | 250               | 150   | 8   | 250               | 150   | 16  | 350               | 150   | 16  | 350               | 150   |     |                   |       |     |                   |       |

| XC7K355T             |     |                   |       |     |                   |       |     |                   |       |     |                   |       |     |                   |       | 24  | 300               | 0     |     |                   |       |

| XC7K410T             |     |                   |       | 8   | 250               | 150   | 8   | 250               | 150   | 16  | 350               | 150   | 16  | 350               | 150   |     |                   |       |     |                   |       |

| XC7K420T             |     |                   |       |     |                   |       |     |                   |       |     |                   |       |     |                   |       | 28  | 380               | 0     | 32  | 400               | 0     |

| XC7K480T             |     |                   |       |     |                   |       |     |                   |       |     |                   |       |     |                   |       | 28  | 380               | 0     | 32  | 400               | 0     |

- 1. 記載されているパッケージはすべて鉛フリーです (FBG、FFG には例外項目 No. 15 が適用される)。一部は鉛パッケージでも入手可能です。

- 2. FBG676 と FFG676 のデバイスは、フットプリントに互換性があります。

- 3. FBG900 と FFG900 のデバイスは、フットプリントに互換性があります。

- 4. FB パッケージの GTX トランシーバーは、FBG484 では最大 10.3Gb/s のデータ レート、FBG676 および FBG900 では最大 6.6Gb/s のデータ レートをサポートします。詳細は、『Kintex-7 FPGA データシート: DC 特性および AC スイッチ特性』(DS182: <u>英語版</u>、<u>日本語版</u>) を参照してください。

- 5. HR は High Range I/O で、1.2V から 3.3V の I/O 電圧をサポートします。

- 6. HP は High Performance I/O で、1.2V から 1.8V の I/O 電圧をサポートします。

## Virtex-7 FPGA の機能一覧

#### 表 8: Virtex-7 FPGA の機能一覧

| デバイス <sup>(1)</sup> | ロジック      | コンフィ<br>ロジック<br>(C       | ギャラブル<br>プロック<br>CLB) | DSP<br>スライ<br>ス <sup>(3)</sup> | ブロック  | カ RAM ラ | ロック <sup>(4)</sup> | CMT( | PCIe | GT<br>X | GT<br>H | GT<br>Z | XADC<br>ブロッ | 総 I/O<br>バンク | 最大<br>ユー<br>ザー<br>I/O <sup>(8)</sup> | SLR <sup>(9)</sup> |

|---------------------|-----------|--------------------------|-----------------------|--------------------------------|-------|---------|--------------------|------|------|---------|---------|---------|-------------|--------------|--------------------------------------|--------------------|

|                     | セル        | スライ<br>ス数 <sup>(2)</sup> | 最大分散<br>RAM (Kb)      | ス(3)                           | 18Kb  | 36Kb    | 最大<br>(Kb)         | - /  | (3)  | ^       |         |         | ク           | (7)          | I/O <sup>(8)</sup>                   |                    |

| XC7V585T            | 582,720   | 91,050                   | 6,938                 | 1,260                          | 1,590 | 795     | 28,620             | 18   | 3    | 36      | 0       | 0       | 1           | 17           | 850                                  | N/A                |

| XC7V2000T           | 1,954,560 | 305,400                  | 21,550                | 2,160                          | 2,584 | 1,292   | 46,512             | 24   | 4    | 36      | 0       | 0       | 1           | 24           | 1,200                                | 4                  |

| XC7VX330T           | 326,400   | 51,000                   | 4,388                 | 1,120                          | 1,500 | 750     | 27,000             | 14   | 2    | 0       | 28      | 0       | 1           | 14           | 700                                  | N/A                |

| XC7VX415T           | 412,160   | 64,400                   | 6,525                 | 2,160                          | 1,760 | 880     | 31,680             | 12   | 2    | 0       | 48      | 0       | 1           | 12           | 600                                  | N/A                |

| XC7VX485T           | 485,760   | 75,900                   | 8,175                 | 2,800                          | 2,060 | 1,030   | 37,080             | 14   | 4    | 56      | 0       | 0       | 1           | 14           | 700                                  | N/A                |

| XC7VX550T           | 554,240   | 86,600                   | 8,725                 | 2,880                          | 2,360 | 1,180   | 42,480             | 20   | 2    | 0       | 80      | 0       | 1           | 16           | 600                                  | N/A                |

| XC7VX690T           | 693,120   | 108,300                  | 10,888                | 3,600                          | 2,940 | 1,470   | 52,920             | 20   | 3    | 0       | 80      | 0       | 1           | 20           | 1,000                                | N/A                |

| XC7VX980T           | 979,200   | 153,000                  | 13,838                | 3,600                          | 3,000 | 1,500   | 54,000             | 18   | 3    | 0       | 72      | 0       | 1           | 18           | 900                                  | N/A                |

| XC7VX1140T          | 1,139,200 | 178,000                  | 17,700                | 3,360                          | 3,760 | 1,880   | 67,680             | 24   | 4    | 0       | 96      | 0       | 1           | 22           | 1,100                                | 4                  |

| XC7VH580T           | 580,480   | 90,700                   | 8,850                 | 1,680                          | 1,880 | 940     | 33,840             | 12   | 2    | 0       | 48      | 8       | 1           | 12           | 600                                  | 2                  |

| XC7VH870T           | 876,160   | 136,900                  | 13,275                | 2,520                          | 2,820 | 1,410   | 50,760             | 18   | 3    | 0       | 72      | 16      | 1           | 6            | 300                                  | 3                  |

- 1. EasyPath™-7 FPGA は、短時間でシンプルに、かつリスク フリーでコストを Virtex-7 T および Virtex-7 XT FPGA デザイン向けに削減するソリューションを提供します。

- 2. 7シリーズ FPGA の各スライスには、4つの LUT と 8つのフリップフロップが含まれ、一部のスライスでのみ LUT を分散 RAM または SRL として使用できます。

- 3. 各 DSP スライスには 25 × 18 乗算器、加算器、アキュムレータが 1 つずつ含まれます。

- 4. ブロック RAM は基本的に 36Kb ですが、2 つの独立した 18Kb ブロックとしても使用できます。

- 5. 各 CMT には MMCM と PLL が 1 つずつ含まれます。

- 6. Virtex-7 T FPGA の PCI Express 用インターフェイス ブロックは最高×8 Gen 2 をサポートします。Virtex-7 XT および Virtex-7 HT の PCIe 用インターフェイス ブロックは最高で×8 Gen 3 をサポートします (ただし、XC7VX485T デバイスは×8 Gen 2 をサポート)。

- 7. コンフィギュレーション バンク 0 は含まれません。

- 8. 記載の数値に GTX、GTH、または GTZ トランシーバーは含まれません。

- 9. SLR (Super Logic Region) は、SSI テクノロジを使用する FPGA の構成要素の一部です。Virtex-7 HT デバイスでは SSI テクノロジによって SLR と 28.05Gb/s トランシーバーが接続されています。

### 表 9: Virtex-7 デバイスとパッケージの各組み合わせにおける最大 I/O 数

| パッケージ <sup>(1)</sup> |     | FFG  | 1157              |                   |     | FFG <sup>-</sup> | 1761 <sup>(2)</sup> |                   |     | FHG  | 1761 <sup>(2)</sup> |                   |     | FLG192            | 5                 |

|----------------------|-----|------|-------------------|-------------------|-----|------------------|---------------------|-------------------|-----|------|---------------------|-------------------|-----|-------------------|-------------------|

| サイズ (mm)             |     | 35   | x 35              |                   |     | 42.5             | x 42.5              |                   |     | 45   | x 45                |                   |     | 45 x 45           | ;                 |

| ボール ピッチ              |     | 1    | .0                |                   |     | 1                | 1.0                 |                   |     | 1    | 1.0                 |                   |     | 1.0               |                   |

|                      | GTX | GTH  | I/                | 0                 | GTX | GTH              | I/                  | 0                 | GTX | GTH  | I/                  | 0                 | GTX | I/                | 0                 |

| デバイス                 | GIX | GIII | HR <sup>(3)</sup> | HP <sup>(4)</sup> | GIX | GIII             | HR <sup>(3)</sup>   | HP <sup>(4)</sup> | GIX | GIII | HR <sup>(3)</sup>   | HP <sup>(4)</sup> | GIX | HR <sup>(3)</sup> | HP <sup>(4)</sup> |

| XC7V585T             | 20  | 0    | 0                 | 600               | 36  | 0                | 100                 | 750               |     |      |                     |                   |     |                   |                   |

| XC7V2000T            |     |      |                   |                   |     |                  |                     |                   | 36  | 0    | 0                   | 850               | 16  | 0                 | 1,200             |

| XC7VX330T            | 0   | 20   | 0                 | 600               | 0   | 28               | 50                  | 650               |     |      |                     |                   |     |                   |                   |

| XC7VX415T            | 0   | 20   | 0                 | 600               |     |                  |                     |                   |     |      |                     |                   |     |                   |                   |

| XC7VX485T            | 20  | 0    | 0                 | 600               | 28  | 0                | 0                   | 700               |     |      |                     |                   |     |                   |                   |

| XC7VX550T            |     |      |                   |                   |     |                  |                     |                   |     |      |                     |                   |     |                   |                   |

| XC7VX690T            | 0   | 20   | 0                 | 600               | 0   | 36               | 0                   | 850               |     |      |                     |                   |     |                   |                   |

| XC7VX980T            |     |      |                   |                   |     |                  |                     |                   |     |      |                     |                   |     |                   |                   |

| XC7VX1140T           |     |      |                   |                   |     |                  |                     |                   |     |      |                     |                   |     |                   |                   |

#### 注記:

- 1. 記載されているパッケージはすべて鉛フリーです (FFG、FHG、FLG には例外項目 No. 15 が適用される)。一部は鉛パッケージでも入手可能です。

- 2. FFG1761 と FHG1761 のデバイスは、フットプリントに互換性があります。

- 3. HR は High Range I/O で、1.2V から 3.3V の I/O 電圧をサポートします。

- 4. HP は High Performance I/O で、1.2V から 1.8V の I/O 電圧をサポートします。

#### 表 10: Virtex-7 デバイスとパッケージの各組み合わせにおける最大 I/O 数

| パッケージ <sup>(1)</sup> | FI  | FG115   | 58             | FF  | G1926  | 3 <mark>(2)</mark> | FL  | G1926  | 3 <mark>(2)</mark> | F   | FG192  | 27               | FF  | G1928   | 3(3)           | FL  | G192   | g( <del>3</del> ) | FF  | G193   | 0(4)      | FL  | G193   | 0(4)      |

|----------------------|-----|---------|----------------|-----|--------|--------------------|-----|--------|--------------------|-----|--------|------------------|-----|---------|----------------|-----|--------|-------------------|-----|--------|-----------|-----|--------|-----------|

| サイズ (mm)             | 3   | 35 x 35 | 5              | 4   | 15 x 4 | 5                  | 4   | 15 x 4 | 5                  | 4   | 15 x 4 | 5                | 4   | 15 x 48 | 5              | 4   | 15 x 4 | 5                 |     | 45 x 4 | 5         |     | 45 x 4 | 5         |

| ボール<br>ピッチ           |     | 1.0     |                |     | 1.0    |                    |     | 1.0    |                    |     | 1.0    |                  |     | 1.0     |                |     | 1.0    |                   |     | 1.0    |           |     | 1.0    |           |

|                      |     |         | I/O            |     |        | I/O                |     |        | I/O                |     |        | I/O              |     |         | I/O            |     |        | I/O               |     |        | I/O       |     |        | I/O       |

| デバイス                 | GTX | GTH     | <del>1</del> 6 | GTX | GTH    | 윤                  | GTX | GTH    | <b>₽</b> (5)       | GTX | GTH    | H <sub>(5)</sub> | GTX | GTH     | <del>1</del> 6 | GTX | GTH    | HP<br>(5)         | GTX | GTH    | HP<br>(5) | GTX | GTH    | HP<br>(5) |

| XC7V585T             |     |         |                |     |        |                    |     |        |                    |     |        |                  |     |         |                |     |        |                   |     |        |           |     |        |           |

| XC7V2000T            |     |         |                |     |        |                    |     |        |                    |     |        |                  |     |         |                |     |        |                   |     |        |           |     |        |           |

| XC7VX330T            |     |         |                |     |        |                    |     |        |                    |     |        |                  |     |         |                |     |        |                   |     |        |           |     |        |           |

| XC7VX415T            | 0   | 48      | 350            |     |        |                    |     |        |                    | 0   | 48     | 600              |     |         |                |     |        |                   |     |        |           |     |        |           |

| XC7VX485T            | 48  | 0       | 350            |     |        |                    |     |        |                    | 56  | 0      | 600              |     |         |                |     |        |                   | 24  | 0      | 700       |     |        |           |

| XC7VX550T            | 0   | 48      | 350            |     |        |                    |     |        |                    | 0   | 80     | 600              |     |         |                |     |        |                   |     |        |           |     |        |           |

| XC7VX690T            | 0   | 48      | 350            | 0   | 64     | 720                |     |        |                    | 0   | 80     | 600              |     |         |                |     |        |                   | 0   | 24     | 1,000     |     |        |           |

| XC7VX980T            |     |         |                | 0   | 64     | 720                |     |        |                    |     |        |                  | 0   | 72      | 480            |     |        |                   | 0   | 24     | 900       |     |        |           |

| XC7VX1140T           |     |         |                |     |        |                    | 0   | 64     | 720                |     |        |                  |     |         |                | 0   | 96     | 480               |     |        |           | 0   | 24     | 1,100     |

- 1. 記載されているパッケージはすべて鉛フリーです (FFG、FLG には例外項目 No. 15 が適用される)。 一部は鉛パッケージでも入手可能です。

- 2. FFG1926 と FLG1926 のデバイスは、フットプリントに互換性があります。

- 3. FFG1928 と FLG1928 のデバイスは、フットプリントに互換性があります。

- 4. FFG1930 と FLG1930 のデバイスは、フットプリントに互換性があります。

- 5. HP は High Performance I/O で、1.2V から 1.8V の I/O 電圧をサポートします。

#### 表 11: Virtex-7 HT FPGA デバイスとパッケージの各組み合わせにおける最大 I/O 数

| パッケージ <sup>(1)</sup> |      | FLG115  | 5                 |      | FLG193  | 1                 |     | FLG193  | 2                 |

|----------------------|------|---------|-------------------|------|---------|-------------------|-----|---------|-------------------|

| サイズ (mm)             |      | 35 x 35 |                   |      | 45 x 45 |                   |     | 45 x 45 |                   |

| ボール ピッチ              |      | 1.0     |                   |      | 1.0     |                   |     | 1.0     |                   |

|                      | GTH  | GTZ     | I/O               | GTH  | GTZ     | I/O               | GTH | GTZ     | I/O               |

| デバイス                 | GIII | 512     | HP <sup>(2)</sup> | GIII | 512     | HP <sup>(2)</sup> | 5   | GIZ     | HP <sup>(2)</sup> |

| XC7VH580T            | 24   | 8       | 400               | 48   | 8       | 600               |     |         |                   |

| XC7VH870T            |      |         |                   |      |         |                   | 72  | 16      | 300               |

#### 注記:

- 1. 記載されているパッケージはすべて鉛フリーで、例外項目 No. 15 が適用されます。一部は鉛パッケージでも入手可能です

- 2. HP は High Performance I/O で、1.2V から 1.8V の I/O 電圧をサポートします。

## スタックド シリコン インターコネクト (SSI) テクノロジ

ザイリンクスは SSI テクノロジを採用することで、高容量 FPGA を作成するにあたっての多くの難題を解決しています。 SSI テクノロジと実績ある製造およびアセンブリ技術を用いることで、1 つのパッシブ インターポーザー層上で複数の SLR (Super Logic Region) を組み合わせることが可能となり、1 万を超える内部 SLR 接続を持つ FPGA が作成できるようになります。この結果、低レイテンシ、低消費電力で帯域幅の非常に広いコネクティビティが実現されます。Virtex-7 FPGA では 2 つのタイプの SLR が使用されています。1 つは Virtex-7 T デバイスに含まれるロジック集約タイプの SLR で、もう 1 つは Virtex-7 XT および HT デバイスに含まれる DSP/ブロック RAM/トランシーバーが豊富な SLR です。SSI テクノロジにより、従来の製造方式よりも高性能な FPGA が製造できるようになり、量産までの期間が短くリスクも低減された、かつてない最高容量と最高性能を誇る FPGA が実現しました。SLR 間にある数千もの SLL (Super Long Line) 配線リソースおよび超高性能クロック ラインによって、このような高集積度のプログラマブルロジック デバイスであってもデザインがシームレスに接続されます。

## CLB、スライス、および LUT

CLB アーキテクチャの主な特長は次のとおりです。

- 完全な 6 入力ルックアップ テーブル (LUT)

- LUT 内のメモリ機能

- レジスタおよびシフト レジスタ機能

7 シリーズ FPGA のルックアップ テーブル (LUT) は、出力が 1 つの 6 入力 LUT (64 ビット ROM) として、または出力は別々でアドレスまたはロジック入力が共通の 2 つの 5 入力 LUT (32 ビット ROM) として構成できます。各 LUT 出力はオプションとしてフリップフロップでラッチできます。このような LUT が 4 つ、それらのフリップフロップ 8 つ、マルチプレクサー、そして演算キャリーロジックがスライスを構成し、2 つのスライスが CLB (コンフィギャラブル ロジック ブロック) を構成します。各スライスの 8 つのフリップフロップのうち 4 つ (各 LUT から 1 つずつ) は、ラッチとして構成できます。

全スライスの  $25\sim50\%$  が LUT を 64 ビットの分散 RAM として、あるいは 32 ビットのシフト レジスタ (SRL32) か 2 つの SRL16 として使用できます。 最近の合成ツールでは、このような高効率のロジック、演算、およびメモリ機能を活かした合成が実行されます。

## クロック管理

クロック マネージメント アーキテクチャの主な特長は次のとおりです。

- 低スキューのクロック分配を実現する高速バッファーおよび配線

- 周波数合成および位相シフト

- 低ジッターのクロック生成およびジッターのフィルタリング

各7 シリーズ FPGA には最大 24 個の CMT (クロック マネージメント タイル) が含まれ、各 CMT は MMCM (ミックスド モード クロック マネージャー ) と PLL (位相ロック ループ) 1 つずつで構成されています。

フィードバック送信

### MMCM および PLL

MMCM と PLL には共通の特長が多数あります。これらは共に、入力クロックの広範な周波数の合成回路およびジッター フィルターとしての機能を提供します。これらのコンポーネントの中心は、PFD (位相周波数検出回路) からの入力電圧に従って、それを高速化または低速化する VCO (電圧制御オシレーター)です。

MMCM および PLL には入力ジッターのフィルター モードとして、狭帯域モード、広帯域モード、最適化モードの 3 つがあります。狭帯域モードではジッターの減衰が優先され、位相オフセットが最小になりません。広帯域モードでは位相オフセットが優先され、ジッターの減衰が最大にはなりません。最適化モードの場合、ツールによって最適な設定が指定されます。

### MMCM のその他のプログラマブル機能

MMCM は、フィードバック パス (乗算器として機能) または出力パスの 1 つに分数カウンターを持つことができます。これらのカウンターは 1/8 という整数以外の増分をサポートするため、周波数を 8 の倍数で合成できます。

MMCM は、小さな単位で増分させる固定位相シフトまたは動作中に変更可能な位相シフトもサポートします。増分は VCO 周波数に依存し、たとえば  $1600 \mathrm{MHz}$  では  $11.2 \mathrm{ps}$  となります。

### クロック分配

各 7 シリーズ FPGA は異なる 6 タイプのクロック ライン (BUFG、BUFR、BUFIO、BUFH、BUFMR、高性能クロック) を提供し、大きなファンアウト、短い伝搬遅延、非常に小さなスキューなどのさまざまなクロッキング要件に対応します。

#### グローバル クロック ライン

各 7 シリーズ FPGA (XC7S6 と XC7S15 を除く) が備える 32 のグローバル クロック ラインは最大のファンアウトを提供し、全フリップフロップ クロック、クロック イネーブル、セット/リセット、および多数のロジック入力に使用できます。クロック領域には 12 のグローバル クロック ラインがあり、並行ラインのクロック バッファー (BUFH) で駆動されます。これらの BUFH はそれぞれを独立して有効あるいは無効にできることから、ある領域内にあるクロックをオフにでき、これによってクロック領域の消費電力を細かく制御できるようになります。これらのラインはグローバル クロック バッファーで駆動できるだけでなく、グリッチなしでクロックを多重伝送したり、クロック イネーブルとしての機能を果たします。グローバル クロックは、通常 CMT から駆動されるため、基本的なクロック分散遅延が完全に削除されます。

#### リージョナル クロック

リージョナル クロックは、それがある領域の全クロックを駆動できます。領域とは、I/O 50 個分と CLB 50 個分の高さ、およびデバイスの半分の幅を持つエリアと定義されます。7 シリーズ FPGA には  $2\sim24$  の領域があり、すべての領域に 4 つのリージョナル クロックトラックがあります。各リージョナル クロック バッファーは、4 つの CC (クロック兼用) 入力ピンのいずれかから駆動でき、周波数はオプションとして  $1\sim8$  の任意の整数で分周可能です。

#### 1/0 クロック

I/O クロックは非常に高速で、I/O ロジックおよびシリアライザー/デシリアライザー (SerDes) 回路にのみ使用します (「I/O ロジック」 参照)。7 シリーズ デバイスには、低ジッターで高性能なインターフェイス用に MMCM から I/O への直接接続があります。

### ブロック RAM

ブロック RAM の主な特長は次のとおりです。

- 最大ポート幅が 72 ビットのデュアル ポート 36Kb ブロック RAM

- プログラム可能な FIFO ロジック

- オプションとして内蔵型エラー訂正回路

すべての 7 シリーズ FPGA に  $5 \sim 1,880$  個のデュアル ポート ブロック RAM があり、それぞれが 36Kb を格納します。各ブロック RAM には、格納されたデータを共有する以外は完全に独立した 2 つのポートがあります。

#### 同期動作

読み出しまたは書き込みのメモリアクセスは、クロックによって制御されます。すべての入力、データ、アドレス、クロックイネーブル、書き込みイネーブルはレジスタが付きます。クロックなしではいかなる動作も生じません。入力アドレスは常にクロックされ、次の動作までデータを保持します。オプションとしての出力データのパイプラインレジスタは、1サイクル分のレイテンシが増加する代わりに、より高いクロックレートでの動作を可能にします。

書き込み動作中、データ出力は前に保存されたデータまたは新たに書き込まれたデータを反映させるか、変更なしでそのまま維持することができます。

### プログラム可能なデータ幅

各ポートは  $32K \times 1$ 、 $16K \times 2$ 、 $8K \times 4$ 、 $4K \times 9$  (または 8)、 $2K \times 18$  (または 16)、 $1K \times 36$  (または 32)、 $512 \times 72$  (または 64) のいずれかに構成できます。2 つのポートには別々の比率を指定でき、これに対する制限はありません。

各ブロック RAM は完全に独立した 2 つの 18Kb ブロック RAM に分割でき、それぞれを  $16K \times 1 \sim 512 \times 36$  の任意のアスペクト比で構成できます。36Kb ブロック RAM について説明した内容は、分割した各 18Kb ブロック RAM にも当てはまります。

シンプル デュアル ポート (SDP) モードでのみ、18 ビット (18Kb RAM の場合) または 36 ビット (36Kb RAM の場合) 以上のデータ幅 がサポートされます。このモードでは、一方のポートが読み出し専用、もう一方のポートが書き込み専用となります。そして、1 つ (読み出しまたは書き込み) のデータ幅がプログラム可能で、もう 1 つが 32/36 または 64/72 に固定されます。

デュアル ポート 36Kb RAM の場合は両方の幅がプログラム可能です。

2 つの隣接した 36Kb ブロック RAM をカスケード接続し、追加ロジックなしで 64K×1 のデュアル ポート RAM として構成できます。

#### エラー検出および訂正機能

64 ビット幅のブロック RAM は、追加で 8 つのビットのハミング コード ビットを生成、格納、そして使用でき、読み出し中にシングル ビット エラーの訂正、ダブル ビット エラーの検出 (ECC) を実行します。ECC ロジックは  $64 \sim 72$  ビット幅の外部メモリへの書き込み、またはそのメモリからの読み出しにも使用できます。

#### FIFO コントローラー

シングル クロック (同期) またはデュアル クロック (非同期/マルチレート) 動作に対応する内蔵型の FIFO コントローラーは、内部アドレス値を増分させ、Full、Empty、Almost Full、Almost Empty の 4 つのフラグを提供します。Almost Full および Almost Empty フラグは自由にプログラムできます。ブロック RAM と同様に、FIFO の幅およびワード数はプログラム可能ですが、書き込みポートと読み出しポートの幅は常に同一です。

First-Word Fall-Through モードでは、最初の読み出し前でも最初に書き込まれたワードがデータ出力に現れます。そして、最初のワードが読み出された後は、通常モードと同様に動作します。

## デジタル信号処理 - DSP スライス

DSP の主な特長は次のとおりです。

- 25 × 18 の 2 の補数乗算器/48 ビットの高分解能アキュムレータによる信号処理

- 対称フィルターアプリケーションに最適化され、消費電力を抑えることが可能な前置加算器

- その他の高度な機能: パイプライン化オプション、ALU オプション、専用カスケード接続

DSP アプリケーションは、専用の DSP スライスに最適に実装された多数のバイナリ乗算器およびアキュムレータを使用します。すべての 7 シリーズ FPGA は、専用で完全にカスタマイズされた低消費電力 DSP スライスを数多く装備し、システム デザインの柔軟性を維持しながら、高速処理および小型化を実現しています。

各 DSP スライスは基本的に、専用の  $25 \times 18$  ビット 2 の補数乗算器および 48 ビット アキュムレータで構成され、これらは共に 741 MHz での動作を可能にする性能を持ちます。乗算器は動作中にバイパスでき、2 つの 48 ビット入力は SIMD (単一命令複数データ) 演算ユニット (デュアルの 24 ビット加算/減算/累算、またはクワッドの 12 ビット加算/減算/累算)、またはオペランドが 2 つの 10 個の異なるロジック ファンクションから任意の 1 つを作成可能なロジック ユニットに入力できます。

DSP には、通常対称フィルターに使用される前置加算器が追加されています。この加算器により、高密度に実装されたデザインの性能が向上し、DSP スライス数が最大 50% 削減されます。また、収束丸め (偶数丸めとも呼ばれる) あるいは対称丸めに使用できる 48 ビット幅のパターン検出回路も備えています。パターン検出回路をロジック ユニットと併用する場合には、96 ビット幅のロジック ファンクションが実装可能です。

DSP スライスは多数のパイプラインおよび拡張性能を提供し、デジタル信号処理だけでなくその他多くのアプリケーションで速度と効率性を向上させます。このようなアプリケーションには、バス幅の広いダイナミック シフター、メモリ アドレス ジェネレーター、多入 カマルチプレクサー、メモリ マップされた I/O レジスタ ファイルが含まれます。また、アキュムレータは同期のアップ/ダウン カウンターとしても使用可能です。

## 入力/出力

入力/出力の主な特長は次のとおりです。

- 最高 1,866Mb/s の DDR3 インターフェイスをサポートする高性能 SelectIO テクノロジ

- シグナル インテグリティを向上させたパッケージに高周波数デカップリング キャパシタを搭載

- 低消費電力かつ高速な I/O 動作用にトライステートにすることができるデジタル制御インピーダンス

I/O ピン数は、デバイスおよびパッケージ サイズによって異なります。各 I/O ピンはコンフィギュレーション可能で、多数の規格に準拠しています。電源ピンおよび一部のコンフィギュレーション専用ピンを除き、すべてのパッケージ ピンは同一の I/O 性能を持ち、特定のバンク規則によってのみ制約されます。7シリーズ FPGA の I/O は High Range (HR) または High Performance (HP) のいずれかに分類されます。HR I/O は、 $1.2 \sim 3.3$ V までの最も広範な I/O 電圧をサポートします。HP I/O は最高性能の動作向けに最適化されており、 $1.2 \sim 1.8$ V の電圧をサポートします。

7シリーズ FPGA の HR および HP I/O ピンは、バンクごとに 50 ピンずつ分割されています。各バンクには 1 つの共通  $V_{CCO}$  出力電源があり、これは特定の入力バッファーにも電源を供給します。一部のシングルエンドの入力バッファーには、内部生成の、あるいは外部に基準電圧  $(V_{REF})$  が必要です。バンクあたり 2 つの  $V_{REF}$  ピンがありますが (コンフィギュレーション バンク 0 は除く)、1 つのバンクで使用できる  $V_{REF}$  電圧値は 1 つのみです。

ザイリンクス 7 シリーズ FPGA は、最もコストが低いスモール フォーム ファクターのワイヤボンド パッケージ、高性能な従来型のフリップチップ パッケージ、スモール フォーム ファクターと高性能のバランスを兼ね備えるリッドなしのフリップチップ パッケージまで、ユーザーのニーズに応える多様なパッケージで入手可能です。フリップチップ パッケージの場合、シリコン デバイスは高度なフリップチップ プロセスでパッケージ サブストレートに実装されます。ESR 調整キャパシタがパッケージ上に分散して搭載されており、これによって同時スイッチング出力 (SSO) が生じる条件下でのシグナル インテグリティが最適化されます。

#### I/O 電気特性

シングルエンド出力は従来型の CMOS プッシュ/プル出力構造を使用するもので、 $V_{CCO}$  は High を、グランドは Low を駆動し、ハイインピーダンス状態も可能です。システム設計者はスルー レートおよび駆動能力を指定できます。入力は常にアクティブですが、出力がアクティブの間は通常無視されます。また、各ピンはオプションとして、弱いプルアップまたはプルダウン抵抗を付けることができます。

ほとんどの信号ピン ペアが、差動入力ペアまたは出力ペアとして構成できます。さらに、差動入力ペアを  $100\Omega$  の内部抵抗で終端できるオプションもあります。7 シリーズのすべてのデバイスは LVDS 以外の差動規格としてRSDS、BLVDS、差動 SSTL、差動 HSTL をサポートします。

各 I/O は、シングルエンドおよび差動の HSTL、SSTL などのメモリ I/O 規格をサポートします。SSTL I/O 規格は、データ レートが 1.866Mb/s までの DDR3 インターフェイス アプリケーションをサポート可能です。

### トライステート型デジタル制御インピーダンスおよび低消費電力 I/O 機能

トライステート型デジタル制御インピーダンス (T\_DCI) は、出力駆動インピーダンス (直列終端) を制御したり、あるいは  $V_{CCO}$  に対して入力信号を並列終端、 $V_{CCO}/2$  に対して分割 (テブナン) 終端を構成可能です。 $T_DCI$  を使用した信号には、オフチップの終端は不要です。これはボード スペースを節約するだけでなく、出力モードまたはトライステートの場合に終端が自動的にオフになるため、オフチップ終端の消費電力も大幅に削減されます。さらに、I/O の IBUF および IDELAY には低電力モードがあり、特にメモリ インターフェイスの実装時に、低消費電力化を図ることができます。

### I/O ロジック

### 入力および出力遅延

すべての入力および出力は組み合わせ、またはレジスタ付きとして設定でき、ダブルデータレート (DDR) が全入力および出力でサポートされています。すべての入力および一部の出力は、それぞれを 78ps、52ps、または 39ps 単位で最大 32 タップ分個別に遅延させることができ、この遅延は IDELAY および ODELAY としてインプリメントされます。遅延ステップ数はコンフィギュレーションで設定できますが、使用中にも増加または減少させることが可能です。

### ISERDES および OSERDES

アプリケーションの多くは、デバイス内部で高速なビット シリアル I/O とより低速なパラレル動作を組み合わせます。これには、I/O 構造内にシリアライザーおよびデシリアライザー (SerDes) が必要です。各 I/O ピンには8 ビットの IOSERDES (ISERDES & OSERDES) があり、I/O と、I/O 3、I/O 4、I/O 5、I/O 6、I/O 6、I/O 6、I/O 7、または8 ビットの幅 (プログラム可能) でシリアルからパラレル、あるいはパラレルからシリアルへデータを変換します。 さらに、I/O 7 (通常は差動 I/O) からの IOSERDES 6 I/O 7 (可能ない変換がサポートされます。ISERDES 6 には、I/O 6 (ログラム可能) 1.25 I/O 6 (ログラムの I/O 7 (ログラム I/O 7 (ログ) 1 (ログ I/O 7 (ログ I/O 7 (ログ) 1 (ログ) 1 (ログ I

### 低電力ギガビット トランシーバー

低電力ギガビットトランシーバーの主な特長は次のとおりです。

- 最高 6.6Gb/s (GTP)、12.5Gb/s (GTX)、13.1Gb/s (GTH)、または 28.05Gb/s (GTZ) のライン レート (デバイス ファミリによる) で動作し、シングル デバイスで 400G インプリメンテーションを実現

- チップ間インターフェイス用に最適化された低電力モード

- 高性能な送信プリエンファシスおよびポストエンファシス、受信リニア イコライザー (CTLE)、長距離伝送やバックプレーン アプリケーション用の判定帰還等化 (DFE)。シリアル リンクの調整を容易にするレシーバーのイコライゼーションでの自動適応およびオンチップのアイ スキャン

光モジュールへの超高速シリアルデータ転送はもとより、同一 PCB 上の IC 間、バックプレーン経由、あるいはさらに長距離間の超高速シリアルデータ転送が一般的になっており、これらはデータレート 100Gb/s やさらに高速な 400Gb/s まで拡張するカスタム ラインカードを実現する上で重要です。このような転送には、高データレートでのシグナルインテグリティの問題に対応する専用のオンチップ回路および差動 I/O が必要となります。

7 シリーズ FPGA には、Artix-7 ファミリで最大 16 個、Kintex-7 ファミリで最大 32 個、Virtex-7 ファミリで最大 96 個のトランシーバー回路が搭載されています。各シリアルトランシーバーは、トランスミッターとレシーバーの組み合わせで構成されています。7 シリーズのシリアルトランシーバーは、リング オシレーターと LC タンク アーキテクチャの組み合わせを使用でき、GTZ では 1 つの LC タンク アーキテクチャを用いてファミリ間の IP の移植性を維持しながら柔軟性と性能の最適なバランスを実現しています。サポートされる最大データ レートは7 シリーズ ファミリによって異なり、GTP で 6.6Gb/s、GTX で 12.5Gb/s、GTH で 13.1Gb/s、そして GTZ では 28.05Gb/s です。低速なデータ レートは、FPGA ロジックでのオーバーサンプリングによって実現可能です。シリアルトランスミッターおよびレシーバーは高度な PLL アーキテクチャを使用する独立した回路で、基準周波数入力をプログラム可能な 100 までの値で逓倍することでビット シリアル データ クロックを生成します。トランシーバーそれぞれに、ユーザー定義可能な多数の機能およびパラメーターがあります。これらはすべてコンフィギュレーション中に定義でき、その多くは動作中にも変更できます。

### トランスミッター

トランスミッターは基本的に、変換比率が 16、20、32、40、64、または 80 のパラレル/シリアル コンバーターです。さらに GTZ トランスミッターの場合は、最大 160 ビット データ幅をサポートします。このため、データパス幅とタイミング マージンのトレードオフによって高性能が要求されるデザインにも対応できます。トランスミッターの出力は、シングル チャネルの差動出力信号で PC ボードを駆動します。 TXOUTCLK は適切に分周されたシリアル データ クロックで、内部ロジックからのパラレル データを直接ラッチするために使用できます。入力されるパラレル データはオプションの FIFO を通り、十分なデータ遷移が生じるようハードウェアでの 8B/10B、64B/66B、または 64B/67B エンコードがサポートされています。ビット シリアル出力信号は、差動信号によって 2 つのパッケージ ピンを駆動します。この出力信号ペアは、信号振幅幅とプリおよびポストエンファシスがプログラム可能で、PC ボードでの信号ロスやほかのインターコネクト特性を補います。より短いチャネルでは、振幅幅を小さくすることで低消費電力化が可能です。

### レシーバー

レシーバーは基本的に、入力ビット シリアル差動信号をそれぞれ 16、20、32、40、64、または 80 ビット幅のパラレル ストリーム ワードに変換するシリアル/パラレル コンバーターです。さらに GTZ レシーバーの場合は、最大 160 ビット データ幅をサポートします。これにより、内部データ幅とさまざまなロジックのタイミング マージンのバランスの取れた設計が可能になります。レシーバーは入力差動データ ストリームを受け取って、それを (PC ボードやほかのインターコネクト特性を補うため) プログラム可能なリニア イコライザーおよび DFE を介し、基準クロック入力を使用してクロックの認識を開始します。データ パターンは NRZ (Non-Return-to-Zero) エンコードを使用し、オプションとして選択したエンコード方式を用いることで十分なデータ遷移が生じるようにします。パラレル データは RXUSRCLK クロックを使用して FPGA ロジックに転送されます。短いチャネルの場合、トランシーバーを特別な低電力モード (LPM) で使用することで、消費電力が約 30% 削減されます。

### Out-of-Band 信号

トランシーバーは、高速シリアルデータ転送がアクティブでないときに、トランスミッターからレシーバーへ低速の信号を転送するためによく使用される Out-of-Band (OOB) 信号を提供します。通常、リンクがパワー ダウン ステートにあるか初期化されていない場合がこれに該当し、この機能は PCI Express および SATA/SAS のアプリケーションで有用です。

## PCI Express デザイン用統合インターフェイス ブロック

PCI Express 用統合ブロックの主な特長は次のとおりです。

- PCI Express Base Specification 2.1 または 3.0 (デバイス ファミリによる) に準拠し、エンドポイントとルート ポート機能に対応

- Gen1 (2.5Gb/s)、Gen2 (5Gb/s)、および Gen3 (8Gb/s) をサポート (デバイス ファミリによる)

- アドバンス コンフィギュレーション オプション、アドバンス エラー レポート (AER)、および End-to-End CRC (ECRC) のアドバンス エラー レポートと ECRC 機能

- マルチ ファンクションおよび SR-IOV (Single Root I/O Virtualization) をソフトロジック ラッパーを使用してサポートまたはデバイス ファミリによっては統合ブロックに組み込み

すべての Virtex-7 デバイスには、PCI Express Base Specification Revision 2.1 または 3.0 に準拠するよう設計され、エンドポイントまたはルート ポートとしてコンフィギュレーション可能な、PCI Express 用統合ブロックが少なくとも 1 つ搭載されています。ルートポートは、ルート コンプレックス相当の機能を提供し、PCI Express プロトコルを用いた FPGA 間のカスタム通信を可能にするだけでなく、イーサネット コントローラーやファイバー チャネル HBA などの ASSP エンドポイント デバイスを FPGA に接続します。

このブロックはシステム デザイン要件に従うよう高度にコンフィギュレーション可能で、2.5 Gb/s、5.0 Gb/s、および 8.0 Gb/s のデータレートで 1、2、4、または 8 レーンの動作をサポートします。高性能アプリケーション向けには、ブロックを高度にバッファーすることで、1,024 バイトまでの柔軟性に優れた最大ペイロード サイズを提供します。また、シリアル コネクティビティ用に統合された高速トランシーバーと、データ バッファー用にはブロック RAM とインターフェイスします。全体として、これらのエレメントは PCI Express プロトコルの物理層、データ リンク層、そしてトランザクション層をインプリメントします。

ザイリンクスは、さまざまな構築ブロック (PCI Express 用統合ブロック、トランシーバー、ブロック RAM、クロック リソース)をエンドポイントまたはルート ポート ソリューションに活用できるようにする軽量、コンフィギャラブル、かつ簡単に使用できる LogiCORETM IP ラッパーを提供しています。レーン幅、最大ペイロード サイズ、FPGA ロジック インターフェイス速度、基準クロック 周波数、およびベース アドレス レジスタのデコード とフィルタリングなど、数多くのパラメーターをシステム設計者が制御できます。

ザイリンクスは AXI4-Stream およびメモリ マップされた AXI4 用の 2 つのラッパーを提供しています。7 シリーズ デバイスの場合、PCI Express 用統合ブロックで従来の TRN/ローカル リンクは使用できません。AXI4-Stream は、このブロックを既に使用しているデザイン用に設計されたもので、TRN から AXI4-Stream への移行を容易にします。メモリ マップされた AXI4 はザイリンクス Platform Studio/EDK デザイン フローおよび MicroBlaze<sup>TM</sup> プロセッサ ベースのデザイン用に提供されているものです。

PCI Express デザインのソリューションに関する資料および詳細は、http://japan.xilinx.com/products/technology/pci-express.html.

### コンフィギュレーション

ザイリンクス7シリーズ FPGA は、次のような高度なコンフィギュレーション機能を備えています。

- 高速 SPI および BPI (パラレル NOR) コンフィギュレーション

- ビルトイン MultiBoot およびセーフ アップデート機能

- HMAC/SHA-256 認証を使用した 256 ビット AES 暗号化

- ビルトイン **SEU** 検出および訂正

- パーシャル リコンフィギュレーション

ザイリンクス 7 シリーズ FPGA は、カスタマイズしたコンフィギュレーション データを SRAM タイプの内部ラッチに格納します。デバイス サイズとユーザー デザインのインプリメンテーション オプションによって、コンフィギュレーション ビットは最大 450Mb になります。コンフィギュレーション データは揮発性の媒体に格納されるため、FPGA への電源投入ごとに再ロードする必要があります。格納されたデータは、PROGRAM\_B ピンを Low にすることで、随時再ロードできます。コンフィギュレーション データは複数の方法およびデータ形式でロード可能で、これは 3 つのモード ピンで決定します。

SPI インターフェイス (×1、×2、および×4 モード) と BPI インターフェイス (パラレル NOR ×8 および×16) の 2 つは、FPGA のコンフィギュレーションによく使用される方法です。この方法では、ユーザーが SPI または BPI フラッシュを FPGA に直接接続し、FPGA 内部のコンフィギュレーション ロジックがフラッシュからビットストリームを読み出して、その FPGA をコンフィギュレーションします。FPGA がオンザフライで自動的にバス幅を検出するため、外部からの制御や切り替えは不要で、サポートされるバス幅は、SPI では×1、×2、×4、BPI では×8 と×16 です。また、バス幅が広いほど、コンフィギュレーション速度は高くなり、電源を投入してから FPGA が起動するまでに必要な時間が短縮されます。デバイスパッケージの組み合わせによっては、BPI など一部のコンフィギュレーションオプションがサポートされません。詳細は、『7 シリーズ FPGA コンフィギュレーション ユーザー ガイド』(UG470: 英語版、日本語版) を参照してください。

マスター モードの場合、FPGA は内部生成されたクロックからコンフィギュレーション クロックを駆動可能ですが、コンフィギュレーションをより高速で実行するため、外部のコンフィギュレーション クロック ソースを使用することもできます。これにより、マスターモードの使い易さを活かしたコンフィギュレーションが可能になります。一方、最大 32 ビット幅のスレーブ モードもサポートされており、これは特にプロセッサによるコンフィギュレーションの場合に有用です。

FPGA は、SPI または BPI フラッシュを使用して別のイメージでリコンフィギュレーションできるため、外部コントローラーは不要となります。データ送信時にエラーが生じた場合でも、FPGA は元のデザインを再ロードできるため、その処理の最後には動作可能なFPGA としてコンフィギュレーションされます。これは特に、最終的な製品が出荷された後でデザインを更新する際に役立ちます。つまり、初期バージョンのデザインで製品が出荷できるため、製品をいち早く市場に投入できることになります。この機能によって、製品がすでにフィールドにある状態で、最新のデザインをエンドユーザーに提供し続けることが可能となります。

ダイナミック リコンフィギュレーション ポート (DRP) により、システム設計者は、MMCM、PLL、XADC、トランシーバー、PCI Express 用統合ブロックのコンフィギュレーション レジスタおよびステータス レジスタに簡単にアクセスできます。 DRP はメモリにマップされたレジスタのように動作し、ブロック固有のコンフィギュレーション ビット、ステータス レジスタ、制御レジスタへのアクセスおよび変更が可能です。

#### 暗号化、リードバック、パーシャル リコンフィギュレーション

XC7S6 および XC7S15 を除くすべての 7 シリーズ デバイスでは、重要なカスタマー IP を含む FPGA ビットストリームを、256 ビットの AES 暗号化および HMAC/SHA-256 認証を使用して保護し、デザインの不正なコピーを防止します。FPGA はコンフィギュレーション中に、内部に格納された 256 ビットのキーを用いて、これをオンザフライで復号化します。このキーは、バックアップ バッテリ付きの RAM か不揮発性の eFUSE に保存できます。

ほとんどのコンフィギュレーション データは、システム動作に影響を与えることなくリードバック可能です。通常はすべてをコンフィギュレーションするか、まったくコンフィギュレーションしないかのどちらかですが、ザイリンクス 7 シリーズ FPGA はパーシャル リコンフィギュレーションをサポートしています。これは、FPGA の一部のみを変更し、ほかの部分はそのまま維持することを可能にする非常に有益で柔軟性に優れた機能です。設計者はリコンフィギュレーション可能な部分を時分割で処理し、より小さなデバイスにさらに多くの IP を含めることができるため、コストおよび消費電力の削減につながります。パーシャル リコンフィギュレーションを適用できるデザインでは、FPGA の多様性は大幅に向上します。

# XADC (Analog-to-Digital Converter)

XADC アーキテクチャの主な特長は次のとおりです。

- 2個の12ビット、1MSPSのアナログ/デジタルコンバーター(ADC)

- 最大 17 個の柔軟でユーザー コンフィギュレーション可能なアナログ入力

- オンチップ リファレンスまたは外部リファレンスを選択可能

- オンチップの温度 (最大誤差 ±4℃) および電源電圧 (最大誤差 ±1%) センサー

- JTAG を介して連続的に ADC の計測結果にアクセス

すべてのザイリンクス 7 シリーズ FPGA (XC7S6 と XC7S15 を除く) は、XADC と呼ばれる、柔軟性に優れた新しいアナログ インターフェイスを備えています。 7 シリーズ FPGA が持つプログラマブル ロジックの性能と組み合わせることにより、データ取得と計測に関する幅広い要件に対応します。 詳細は、 http://japan.xilinx.com/ams を参照してください。

XADC には専用のトラックおよびホールド アンプを持つ 12 ビットで 1MSPS の ADC が 2 つと、1 つのオンチップ アナログ マルチプレクサー (最大 17 の外部アナログ入力チャネルをサポート)、オンチップ温度/電源電圧センサーが含まれます。2 つの ADC は、2 つの外部アナログ入力チャネルを同時にサンプルするように構成できます。トラックおよびホールド アンプは、単極、双極、差動の幅広いアナログ入力をサポートします。アナログ入力は、1MSPS のサンプルレートで 500KHz 以上の信号帯域幅をサポートします。専用のアナログ入力を用いて外部アナログ マルチプレクサー モードを使用すると、さらに広いアナログ帯域幅をサポートできます (『7 シリーズ FPGA および Zynq-7000 All Programmable SoC XADC デュアル 12 ビット 1MSPS アナログ/デジタルコンバーター ユーザーガイド』 (UG480: 英語版、日本語版)参照)。

XADC は、オプションとしてオンチップの基準回路 (±1%) を使用するため、温度や電源レールの基本的なオンチップ モニタリング用 に外部にアクティブなコンポーネントは必要ありません。ADC の 12 ビットの性能を十分に発揮させるには、外部に 1.25V のリファレンス IC を使用することを推奨します。

XADC をデザインにインスタンシエートしない場合のデフォルトでは、XADC はすべてのオンチップ センサーの出力をデジタル化します。最も新しい計測結果は、最大および最小の測定結果と共に専用のレジスタに格納され、JTAG インターフェイスを介して常時アクセスできます。また、ユーザー定義のアラームしきい値によって超過温度イベントおよび許容外の温度変動を自動的に知らせることができ、ユーザーが指定した制限値 (100°C など) を用いて自動的に電源を切断するようにもできます。

## EasyPath-7 FPGA

EasyPath-7 FPGA は、短時間でシンプルに、かつリスク フリーでコストを削減するソリューションを Kintex-7、Virtex-7 T、および Virtex-7 XT FPGA デザイン向けに提供します。また、同一のパッケージとスピード グレードをサポートし、すべての Kintex-7 または Virtex-7 FPGA データシート仕様において機能とタイミングが一致します。再設計コストや再評価コストが必要ないため、ほかの FPGA コスト削減ソリューションと比較して最も低い総コスト ソリューションを実現します。

## 7 シリーズ FPGA 注文情報

表 12 に、このデバイスファミリで提供されているスピードグレードおよび温度グレードを示します。一部のデバイスでは、入手可能なスピードグレードと温度グレードに制限があります。

### 表 12: 7 シリーズのスピード グレードと温度仕様

|              | デバイス                   | スピード グレード、温度範囲、動作電圧 |                      |                |                |  |

|--------------|------------------------|---------------------|----------------------|----------------|----------------|--|

| デバイス<br>ファミリ |                        | コマーシャル (C)          | 拡張 (E)               | インダストリアル (I)   | エクスパンド (Q)     |  |

|              |                        | 0°C ~ +85°C         | 0°C ~ +100°C         | -40°C ~ +100°C | -40°C ∼ +125°C |  |

| Spartan-7    | すべて                    | -2C (1.0V)          |                      | -2I (1.0V)     |                |  |

|              |                        | -1C (1.0V)          |                      | -1I (1.0V)     | -1Q (1.0V)     |  |

|              |                        |                     |                      | -1LI (0.95V)   |                |  |

|              | すべて                    |                     | -3E (1.0V)           |                |                |  |

| Artix-7      |                        | -2C (1.0V)          |                      | -2I (1.0V)     |                |  |

|              |                        |                     | -2LE (1.0V または 0.9V) |                |                |  |

|              |                        | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

|              |                        |                     |                      | -1LI (0.95V)   |                |  |

|              | XC7K70T                |                     | -3E (1.0V)           |                |                |  |

|              |                        | -2C (1.0V)          |                      | -2I (1.0V)     |                |  |

|              |                        |                     | -2LE (1.0V または 0.9V) |                |                |  |

| ***          |                        | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

| Kintex-7     | XC7K160T               |                     | -3E (1.0V)           |                |                |  |

|              | XC7K325T<br>XC7K355T   | -2C (1.0V)          |                      | -2I (1.0V)     |                |  |

|              | XC7K410T               |                     | -2LE (1.0V または 0.9V) | -2LI (0.95V)   |                |  |

|              | XC7K420T<br>XC7K480T   | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

|              | XC7V585T               |                     | -3E (1.0V)           |                |                |  |

|              |                        | -2C (1.0V)          |                      | -2I (1.0V)     |                |  |

|              |                        |                     | -2LE (1.0V)          |                |                |  |

|              |                        | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

| Virtex-7 T   | XC7V2000T -            | -2C (1.0V)          |                      |                |                |  |

|              |                        |                     | -2GE (1.0V)          |                |                |  |

|              |                        |                     | -2LE (1.0V)          |                |                |  |

|              |                        | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

|              | XC7VX330T              |                     | -3E (1.0V)           |                |                |  |

|              |                        | -2C (1.0V)          |                      | -2I (1.0V)     |                |  |

|              | XC7VX415T<br>XC7VX485T |                     | -2LE (1.0V)          |                |                |  |

|              | XC7VX550T<br>XC7VX690T |                     |                      |                |                |  |

|              | AC/VA0901              | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

|              | XC7VX980T              | -2C (1.0V)          |                      |                |                |  |

| Virtex-7 XT  |                        | <u></u>             | -2LE (1.0V)          |                |                |  |

|              |                        | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

|              | XC7VX1140T             | -2C (1.0V)          |                      |                |                |  |

|              |                        | . ,                 | -2GE (1.0V)          |                |                |  |

|              |                        |                     | -2LE (1.0V)          |                |                |  |

|              |                        | -1C (1.0V)          |                      | -1I (1.0V)     |                |  |

| Virtex-7 HT  | すべて                    | -2C (1.0V)          |                      | , · · · /      |                |  |

|              |                        |                     | -2GE (1.0V)          |                |                |  |

|              |                        |                     | -2LE (1.0V)          |                |                |  |

|              |                        | -1C (1.0V)          | ( . , , )            |                |                |  |

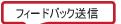

図 1 に Spartan-7 FPGA の注文情報を示します。デバイス パッケージ マーキングの詳細は、『7 シリーズ FPGA パッケージおよびピン配置ガイド』(UG475: 英語版、日本語版) の「パッケージ マーク」を参照してください。

1) -L1 is the ordering code for the lower power, -1L speed grade.

DS180\_01\_012517

#### 図 1: Spartan-7 FPGA の注文情報

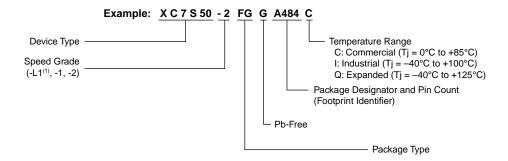

図 2 に示す Artix-7、Kintex-7、および Virtex-7 FPGA の注文情報は、鉛フリー パッケージを含むすべてのパッケージに適用されます。 デバイス パッケージ マーキングの詳細は、『7 シリーズ FPGA パッケージおよびピン配置ガイド』(UG475: 英語版、日本語版) の「パッケージ マーク」を参照してください。

- 1) -L1 is the ordering code for the lower power, -1L speed grade.

- -L2 is the ordering code for the lower power, -2L speed grade.

-G2 is the ordering code for the -2 speed grade devices with higher performance transceivers.

- 4) Some package names do not exactly match the number of pins present on that package. See UG475: 7 Series FPGAs Packaging and Pinout User Guide for package details.

DS180\_01\_061317

図 2: Artix-7、Kintex-7、Virtex-7 FPGA の注文情報

# 改訂履歴

次の表に、この文書の改訂履歴を示します。

| 日付          | バージョン | 内容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2010年6月21日  | 1.0   | 初版                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2010年7月30日  | 1.1   | 暗号化認証の説明に SHA-256 を追加。表 $5$ および表 $7$ で Virtex- $7$ FPGA デバイスとパッケージ の各組み合わせにおける最大 $I/O$ 数 (Virtex- $7$ T デバイス) を更新し、表 $9$ にボール ピッチ情報を 追加してバンク電圧情報を更新。表 $8$ の DSP およびロジック スライス情報と「低電力ギガビットトランシーバー」を更新。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2010年9月24日  | 1.2   | 4.7TMACS DSP を 5.0TMACS DSP に更新 (「概要」)。注記 1 を追加、Kintex-7 および Virtex-7 ファミリの DSP 最大処理速度を更新 (表 1)。 XC7A175T および XC7A355T の CMT 数を更新 (表 4)。 XC7K120T を XC7K160T に、 XC7K230T を XC7K325T に変更し、それぞれ対応する情報を更新 (表 6)。また、3 つのデバイス (XC7K355T、XC7K420T、および XC7K480T) を追加。 XC7K230T を XC7K325T に変更 (表 7)。 XC7V450T のロジック セル、CLB、ブロック RAM、および PCI の情報を更新、XC7VX415T のスライス情報を更新、XC7V1500T および XC7V2000T のブロック RAM 情報を更新、XC7VX605T を XC7VX575T に、 XC7VX895T を XC7VX850T に、 XC7VX910T を XC7VX865T に変更し、それぞれ対応する情報を更新 (表 8)。「デジタル信号処理 - DSP スライス」に記載の処理速度を 640MHz に更新。「Out-of-Band 信号」から特定のトランシーバー名を削除。「Out-of-Band 信号」から特定のトランシーバー名を削除。Virtex-7 FPGA デバイスとパッケージの各組み合わせにおける最大 I/O 数の表 (Virtex-7 T デバイス) で、 XC7VX605T を XC7VX575T に変更し、注記 2 および注記 3 を追加。 XC7VX605T を XC7VX895T を XC7VX850T に、 XC7VX865T に変更 (表 9)。 |

| 2010年10月20日 | 1.3   | XC7K120T を XC7K160T に変更 (表 7)。「デジタル信号処理 - DSP スライス」を更新。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2010年11月17日 | 1.4   | 「概要」で最大 I/O 帯域幅を 3.1Tb/s に修正。「7 シリーズ FPGA の特長」および表 1 で、Virtex-7 FPGA のトランシーバーの最大速度を更新。表 1 および「デジタル信号処理 - DSP スライス」で、DSP の最大処理速度を更新。表 7 で、XC7K70T I/O の情報を更新。表 8 で、XC7VH290T、XC7VH580T、および XC7VH870T デバイスを追加し、XC7V585T、XC7V855T、XC7V1500T、および XC7VX865T デバイスの総 I/O バンク情報を更新。表 9 で、XC7VX415T、XC7VX485T、XC7VX690T、XC7VX850T、および XC7VX865T デバイスの情報を更新。表 11 を追加。GTZトランシーバーの追加も含む「低電力ギガビットトランシーバー」の内容を更新。                                                                                                                                                                                                                                                                                                                                                                                             |

| 2011年2月22日  | 1.5   | 「7 シリーズ FPGA の特長」および「低電力ギガビットトランシーバー」の概要とセクションを更新。表 1 で、Kintex-7 FPGA および Artix-7 FPGA の情報を更新。表 4 で、XC7A175T を更新。また、XC7A355T を更新。表 5 で、3 つの Artix-7 FPGA パッケージ(SBG325、SBG484、および FBG485) を追加、パッケージ FGG784 を FBG784 に変更、XC7A175T および XC7A355T デバイスのパッケージ情報を更新。表 6 で、XC7K160T を更新、3 つのデバイス (XC7K355T、XC7K420T、XC7K480T) を追加。表 7 で、XC7K70T パッケージ情報を更新、3 つのデバイス (XC7K355T、XC7K420T、XC7K480T) を追加。表 8 で、注記 1 (EasyPath FPGA) を追加、注記 7 を更新して GTZ トランシーバーを追加。Virtex-7 FPGA デバイスとパッケージの各組み合わせにおける最大 I/O 数の表 (Virtex-7 T デバイス) で、2 つの Virtex-7 FPGA パッケージ(FHG1157 および FHG1761) を追加、XC7V1500T (FFG1157 なし) および XC7V2000T (FFG1761 なし) のパッケージ情報を更新、さらに関連する注記を削除。「CLB、スライス、および LUT」を追加。「入力/出力」を更新。「EasyPath-7 FPGA」を追加。                                                                                     |

| 2011年3月28日  | 1.6   | 「概要」、「 $7$ シリーズ FPGA の特長」、表 $1$ 、表 $4$ 、表 $5$ 、表 $6$ 、表 $7$ 、表 $8$ 、表 $9$ (Virtex- $7$ $T$ $E$ $XT$ デバイスを $1$ つの表に統合)、および表 $11$ を更新。「低電力ギガビット トランシーバー」のハイライトとセクションを更新。「ブロック RAM」、「PCI Express デザイン用統合インターフェイス ブロック」、「コンフィギュレーション」、「暗号化、リードバック、パーシャル リコンフィギュレーション」、「XADC (Analog-to-Digital Converter)」、「 $7$ シリーズ FPGA 注文情報」、および「EasyPath- $7$ FPGA」を更新。                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2011年7月6日   | 1.7   | 「概要」、「 $7$ シリーズ FPGA の特長」、表 $1$ 、表 $4$ 、表 $6$ 、表 $8$ 、表 $9$ および表 $11$ を更新。表 $10$ を 追加。「スタックド シリコン インターコネクト (SSI) テクノロジ」を追加。「トランスミッター」、「コンフィギュレーション」、および「XADC (Analog-to-Digital Converter)」を更新。図 $1$ を更新。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2011年9月13日  | 1.8   | 「概要」、表 1、表 4、表 5、表 8、「CLB、スライス、および LUT」、「コンフィギュレーション」 および「7 シリーズ FPGA 注文情報」を更新。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 日付          | バージョン  | 内容                                                                                                                                                                                                                                                                               |  |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2012年1月15日  | 1.9    | 「概要」、表 1、表 4、表 5、表 6、表 7、表 8、表 10、表 11、「ブロック RAM」、「デジタル信号 処理 - DSP スライス」、「低電力ギガビット トランシーバー」、「PCI Express デザイン用統合イン ターフェイス ブロック」、「コンフィギュレーション」、「EasyPath-7 FPGA」、および「7 シリーズ FPGA 注文情報」を更新。                                                                                        |  |

| 2012年3月2日   | 1.10   | 「概要」、表 5、および表 12 を更新。                                                                                                                                                                                                                                                            |  |

| 2012年5月2日   | 1.11   | 表 7、表 9、表 10、「低電力ギガビット トランシーバー」、「7 シリーズ FPGA 注文情報」を更新。 「7 シリーズ FPGA 注文情報」を追加。                                                                                                                                                                                                    |  |

| 2012年10月15日 | 1.12   | Artix-7 SL/SLT デバイスについて概要を更新。表 1、表 4、表 5、表 8、表 9、表 10、表 11および表 12 を更新。表 3 を追加。「リージョナル クロック」、「ブロック RAM」、「PCI Express デザイン用統合インターフェイス ブロック」、「コンフィギュレーション」、および「7 シリーズ FPGA 注文情報」を更新。                                                                                                |  |

| 2012年11月30日 | 1.13   | 表 4 と表 12 の注記を更新。「XADC (Analog-to-Digital Converter)」を更新。                                                                                                                                                                                                                        |  |

| 2013年7月29日  | 1.14   | SL および SLT デバイスを削除。「概要」、表 $4$ 、表 $5$ 、表 $6$ および表 $8$ の注記、「リージョナル クロック」、「入力/出力」、「低電力ギガビット トランシーバー」、「PCI Express デザイン用統合インターフェイス ブロック」、「コンフィギュレーション」、「 $7$ シリーズ FPGA 注文情報」を更新。以前の表 $3$ を削除。                                                                                        |  |

| 2014年2月18日  | 1.15   | Preliminary 製品仕様から Production 製品仕様に変更。表 5 の XC7A35T および XC7A50T について、HR I/O の情報を更新。表 8 の XC7VH870T I/O の情報を更新。表 11 を更新。                                                                                                                                                          |  |

| 2014年10月8日  | 1.16   | 表 4 および表 5 に XC7A15T を追加。表 11 から HCG1931 および HCG1932 を削除。「入力および出力遅延」、「ブロック RAM」、「コンフィギュレーション」、「I/O クロック」を更新。表 12 および図 1 を更新。                                                                                                                                                     |  |

| 2014年12月17日 | 1.16.1 | 誤植の修正。                                                                                                                                                                                                                                                                           |  |

| 2015年5月27日  | 1.17   | 表 5、表 7、表 9、表 10、表 11、および図 1 を更新。                                                                                                                                                                                                                                                |  |

| 2016年9月27日  | 2.0    | 表 1, 表 2、表 3、表 12 を含め文書を通して Spartan-7 デバイスを追加。表 4、表 5、表 12 を含め文書を通して 2 つの Artix-7 デバイス (XC7A12T および XC7A25T) を追加。「概要」、図 1、表 7、「リージョナル クロック」、「ブロック RAM」、「PCI Express デザイン用統合インターフェイス ブロック」、「コンフィギュレーション」、「暗号化、リードバック、パーシャル リコンフィギュレーション」、「XADC (Analog-to-Digital Converter)」を更新。 |  |

| 2016年10月20日 | 2.1    | 表 5 を更新。                                                                                                                                                                                                                                                                         |  |

| 2016年12月15日 | 2.2    | 表3を更新。                                                                                                                                                                                                                                                                           |  |

| 2017年3月17日  | 2.3    | 表 1、表 5、表 7、表 9、表 10、表 12、および「I/O 電気特性」を更新。                                                                                                                                                                                                                                      |  |

| 2017年3月28日  | 2.4    | 表7を更新。                                                                                                                                                                                                                                                                           |  |

| 2017年8月1日   | 2.5    | 表 5 および図 2 を更新。                                                                                                                                                                                                                                                                  |  |

## 免責事項

本通知に基づいて貴殿または貴社(本通知の被通知者が個人の場合には「貴殿」、法人その他の団体の場合には「貴社」。以下同じ)に開 示される情報(以下「本情報」といいます)は、ザイリンクスの製品を選択および使用することのためにのみ提供されます。適用される 法律が許容する最大限の範囲で、(1) 本情報は「現状有姿」、およびすべて受領者の責任で(with all faults)という状態で提供され、ザイ リンクスは、本通知をもって、明示、黙示、法定を問わず(商品性、非侵害、特定目的適合性の保証を含みますがこれらに限られませ ん)、すべての保証および条件を負わない(否認する)ものとします。また、(2)ザイリンクスは、本情報(貴殿または貴社による本情報 の使用を含む) に関係し、起因し、関連する、いかなる種類・性質の損失または損害についても、責任を負わない(契約上、不法行為上 (過失の場合を含む)、その他のいかなる責任の法理によるかを問わない) ものとし、当該損失または損害には、直接、間接、特別、付随 的、結果的な損失または損害(第三者が起こした行為の結果被った、データ、利益、業務上の信用の損失、その他あらゆる種類の損失 や損害を含みます) が含まれるものとし、それは、たとえ当該損害や損失が合理的に予見可能であったり、ザイリンクスがそれらの可 能性について助言を受けていた場合であったとしても同様です。ザイリンクスは、本情報に含まれるいかなる誤りも訂正する義務を負 わず、本情報または製品仕様のアップデートを貴殿または貴社に知らせる義務も負いません。事前の書面による同意のない限り、貴殿 または貴社は本情報を再生産、変更、頒布、または公に展示してはなりません。一定の製品は、ザイリンクスの限定的保証の諸条件に 従うこととなるので、japan.xilinx.com/legal.htm#tos で見られるザイリンクスの販売条件を参照して下さい。IP コアは、ザイリンクス が貴殿または貴社に付与したライセンスに含まれる保証と補助的条件に従うことになります。ザイリンクスの製品は、フェイルセーフ として、または、フェイルセーフの動作を要求するアプリケーションに使用するために、設計されたり意図されたりしていません。そ のような重大なアプリケーションにザイリンクスの製品を使用する場合のリスクと責任は、貴殿または貴社が単独で負うものです。 http://japan.xilinx.com/legal.htm#tos で見られるザイリンクスの販売条件を参照してください。

### 自動車用のアプリケーションの免責条項

オートモーティブ製品 (製品番号に「XA」が含まれる) は、ISO 26262 自動車用機能安全規格に従った安全コンセプトまたは余剰性の機能 (「セーフティ設計」) がない限り、エアバッグの展開における使用または車両の制御に影響するアプリケーション (「セーフティアプリケーション」) における使用は保証されていません。顧客は、製品を組み込むすべてのシステムについて、その使用前または提供前に安全を目的として十分なテストを行うものとします。セーフティ設計なしにセーフティアプリケーションで製品を使用するリスクはすべて顧客が負い、製品責任の制限を規定する適用法令および規則にのみ従うものとします。

この資料に関するフィードバックおよびリンクなどの問題につきましては、jpn\_trans\_feedback@xilinx.com まで、または各ページの 右下にある [フィードバック送信] ボタンをクリックすると表示されるフォームからお知らせください。いただきましたご意見を参考に 早急に対応させていただきます。なお、このメール アドレスへのお問い合わせは受け付けておりません。あらかじめご了承ください。